#### Time based quantizers

#### Mootaz ALLAM

#### PhD Student Pierre & Marie Curie University

#### LIP6 Laboratory

Laboratoire d'Informatique de Paris 6

# Time to digital Converters (TDC)

#### **Applications**

- Commercial time-of-flight applications such as Laser range-finding

- Positive electron temography medical imaging technology

- Logic Analyzers

A fundemental element in systems made of closed loop integrated circuits that needs precise control and alignement of timing signals such as :

- Phase Locked Loop (PLL)

- Delay Locked Loop (DLL)

- Clock Data Recovery (CDR)

# Types of Time to Digital Converters

#### 1) Classical TDC

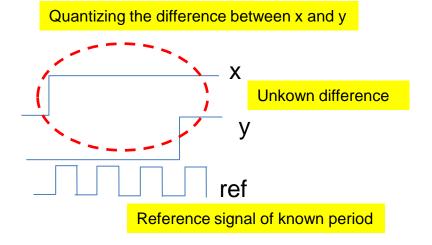

Quantizing the difference in time between 2 signals (PLL, DLL, CDR)

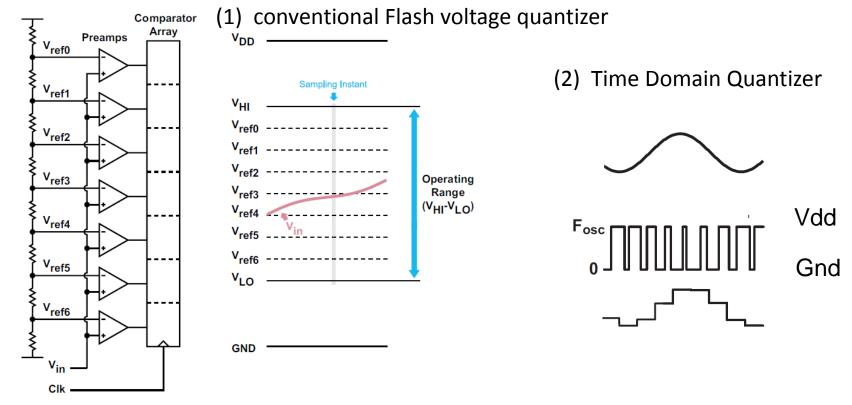

#### 2) TDC as analog signal quantizers

A replacement for traditional voltage quantizers ( High resolution wideband ADC)

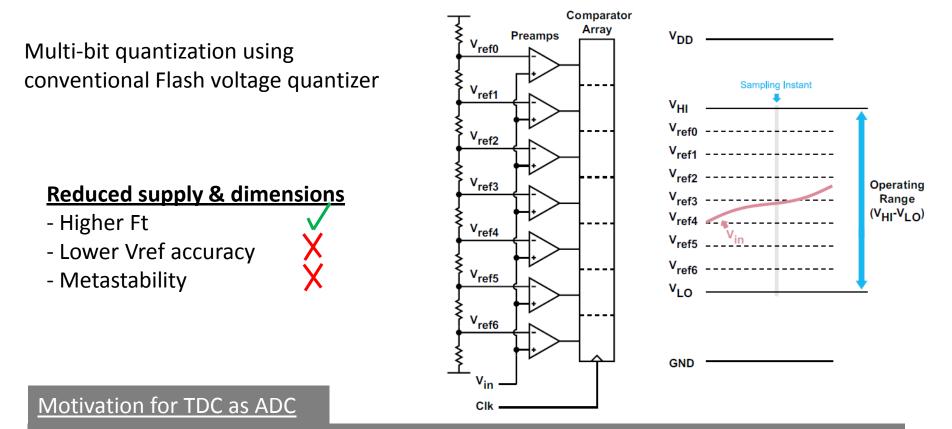

## **Technology Scaling Challenges**

Detecting an edge transition from gnd to Vdd is easier than a voltage step of Vdd/(2^N)

- Only Vdd and gnd are used (low supply compatible)

- High precision detecting transitions (Resolution)

- Mostly digital implementations benefits of tech scaling in terms of power and area

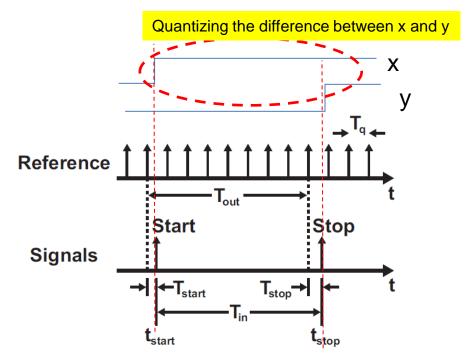

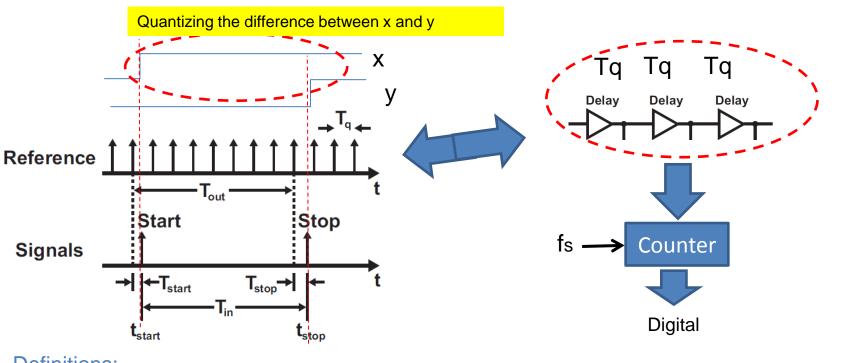

#### Concept of TDC

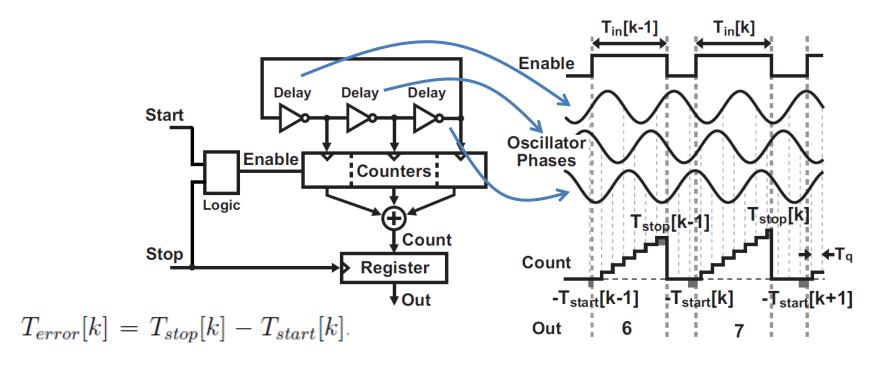

The count of cycles of the reference signal represents the quantized value of Tin

$$T_{error}[k] = T_{stop}[k] - T_{start}[k].$$

$$T_{out}[k] = T_{in}[k] - T_{error}[k],$$

$$Out[k] = \frac{T_{in}[k] - T_{error}[k]}{T_q}.$$

#### Concept of TDC

#### **Definitions:**

TDC resolution : Tq (reference signal period)

TDC Dynamic range: Max\_count\* Tq

- ---- Limited by Technology Min gate delay

- ---- Limited by fs

#### To enhance the TDC resolution:

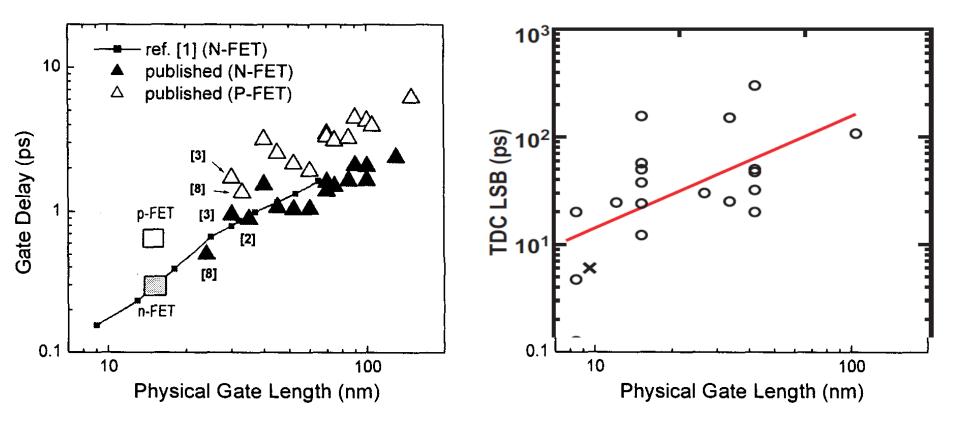

- 1) Technology advancement to lower Technology min gate delay

- 2) Special design techniques to go below Technology min gate delay

# Technology Scaling and TDC resolution

Gate Delay decreases in new technologies and so is the TDC (LSB)

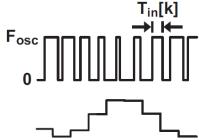

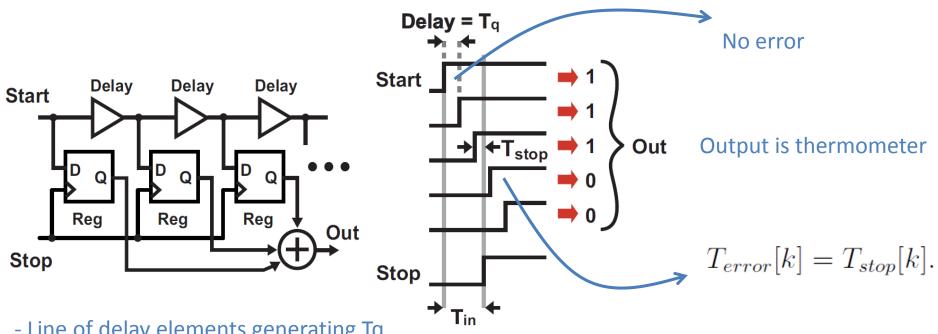

#### 1a) Inverter chain based

- Line of delay elements generating Tg

- Tq propagates through the line

- Registers clocked by the stop signal hold the final value of each delay (thermometer)

- Addition of the registers output gives the quantized value of Tin

For N-bit resolution, the number of delay elements =  $2^N$

- High Cost (area)

- High Power

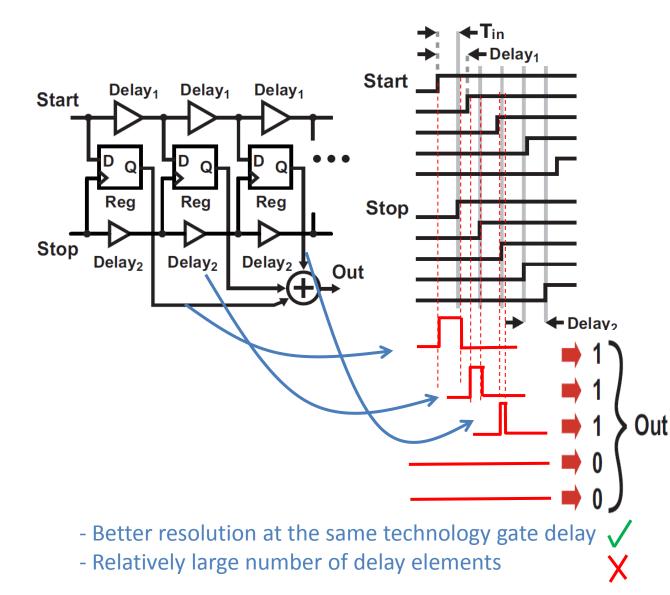

## 1b)Vernier based (T<sub>start</sub> – T<sub>stop</sub> < delay1)

delay1> delay2 Tq=delay1- delay2

Output is thermometer

$$T_{error}[k] = T_{stop}[k].$$

Varying width pulse

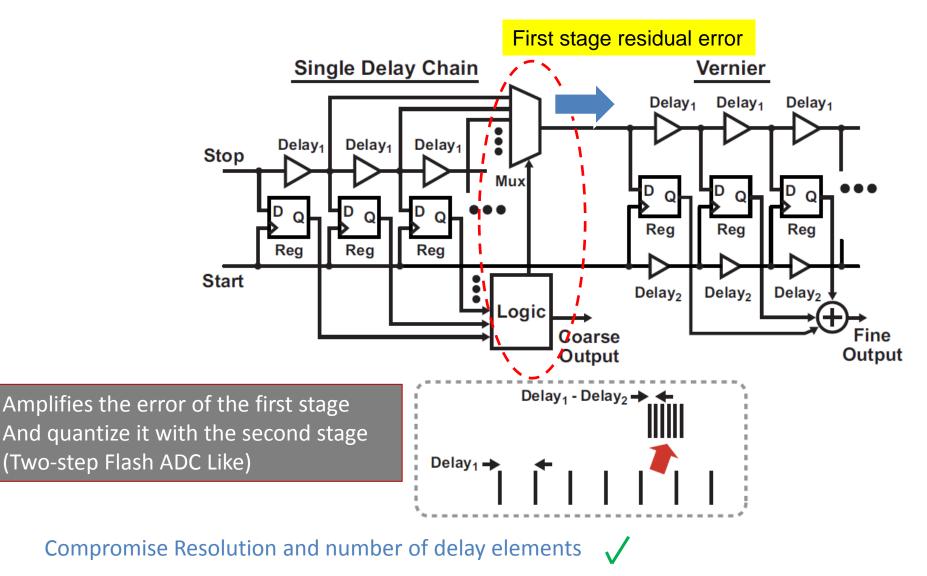

## 1c)Dual Step TDC

### 2a) Oscillator based TDC

Least number of delay elements w.r.t preceding topologies 🗸

Can we have better?

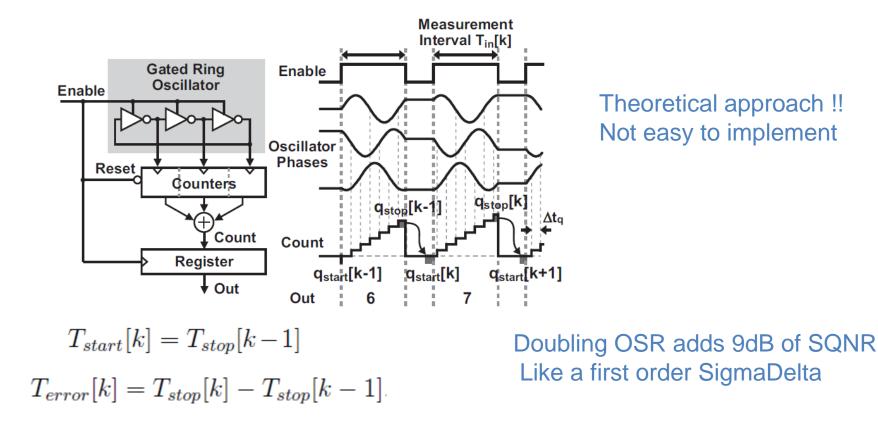

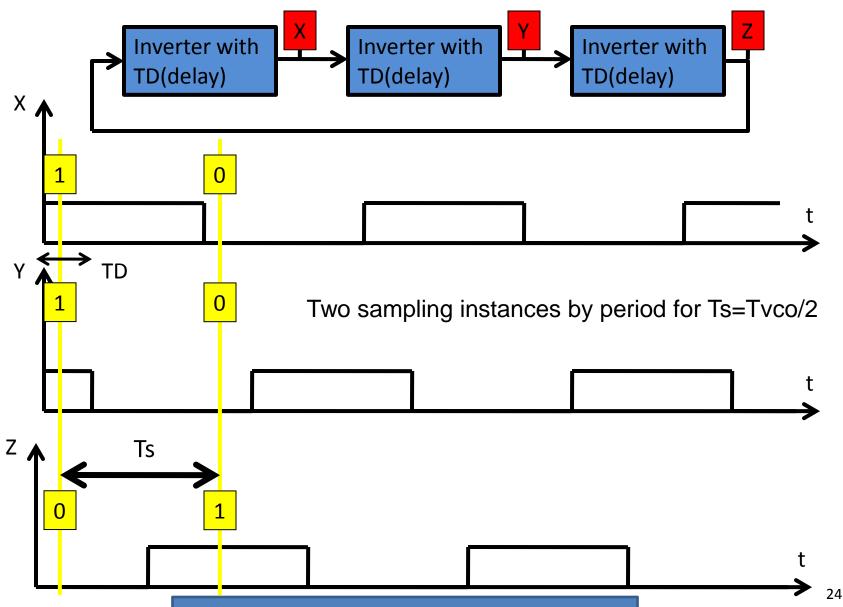

## 2b) Gated Ring Oscillator based TDC

First Order Noise Shaping for both Q and mismatch

Quantization noise is white and performance then is enhanced by oversampling

## Time domain quantizers in ADC

#### Multi-bit quantization using

Motivation for TDC as ADC

Detecting an edge transition from gnd to Vdd is easier than a voltage step of Vdd/(2^N)

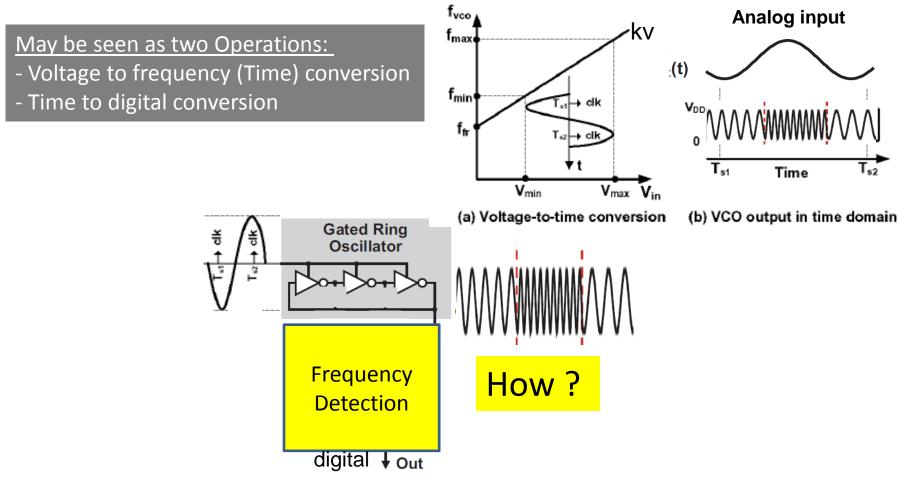

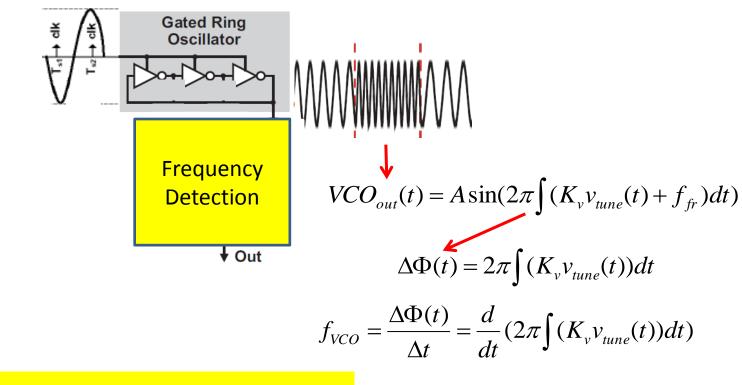

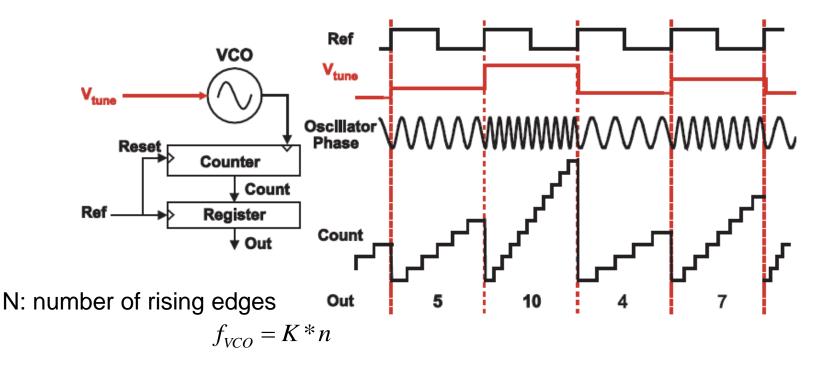

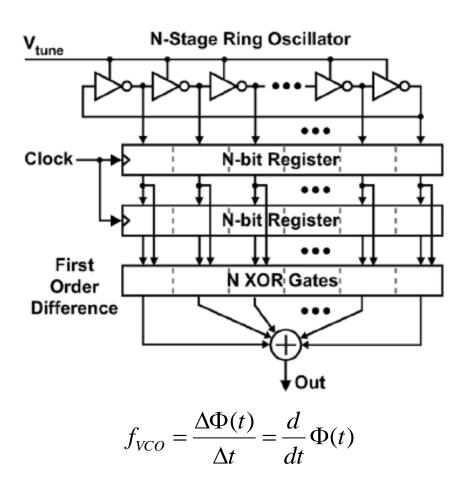

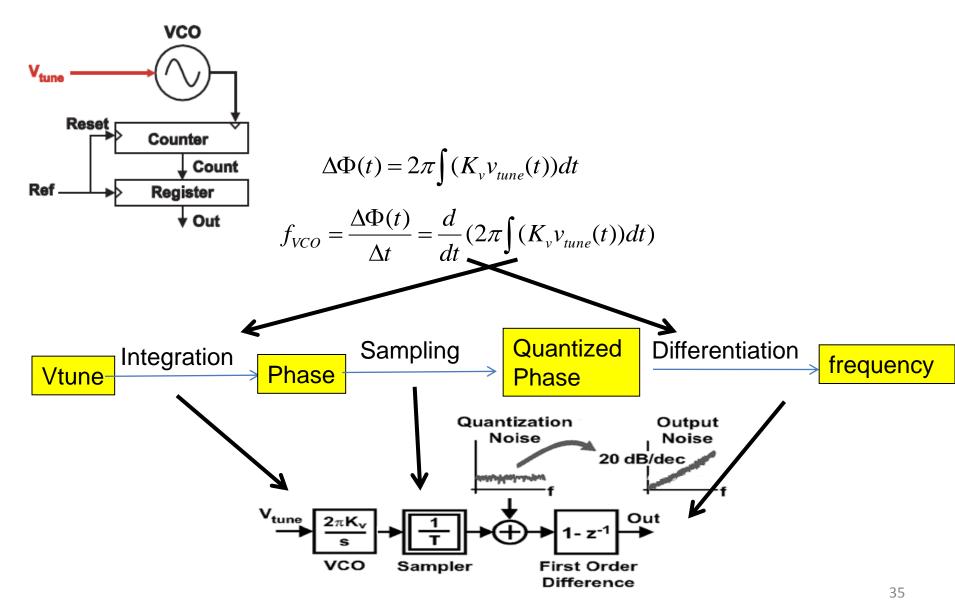

# 3)VCO-based ADC principle

Differences with gated ring oscillator

- The enable signal replaced by analog continuous voltage to be converted

- The oscillator is always running since the input is continuously varying

## 3)VCO-based ADC principle

How to implement this ?

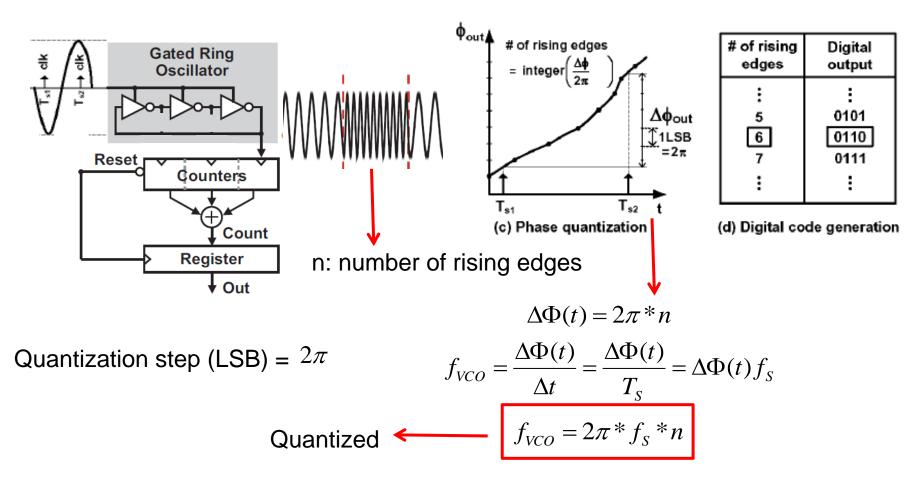

#### 3)VCO-based ADC operation

## 3a)Single phase VCO-based Quantizer

Quantization step (LSB) =  $2\pi$

$f_{VCO} = 0, fs, 2 * fs, ..., (2 - - 1) * fs$

For high resolution, Fvco gets very high to be feasible

n : quantizer resolution

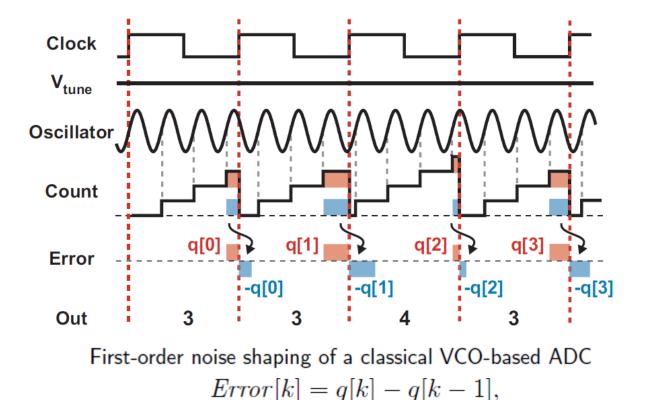

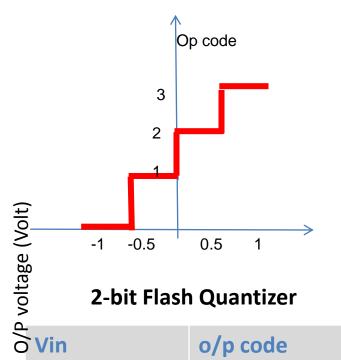

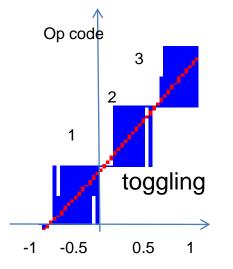

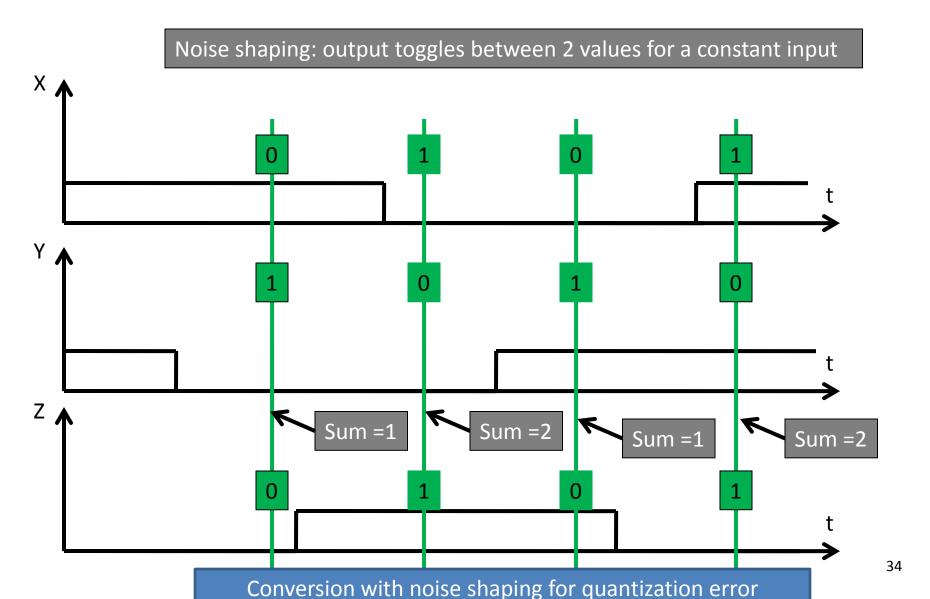

## Noise shaping of VCO-based Quantizer

Constant input and Output is toggling due to residual error memorization

Doubling OSR adds 9dB of SQNR Like a first order Sigma Delta Modulator (SDM°

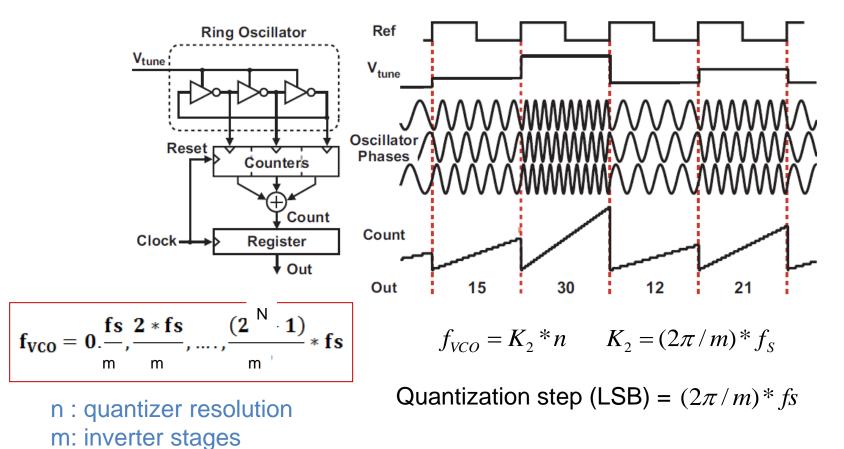

#### 3b)Multi-phase VCO-based Quantizer

Selecting m=  $2^{N-1} \rightarrow fvco_max=fs$

## 3b)Multi-phase VCO-based Quantizer

- 1) Reset pulse can coincide with Ring Clock Pulse(Asynchronous with Reset), Noise shaping will vanish

- 2) Complex implementation for higher OSR and more quantization levels (counters)

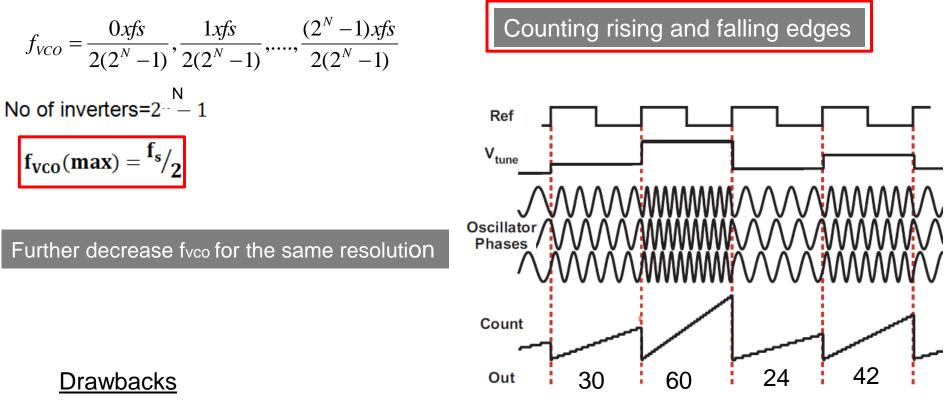

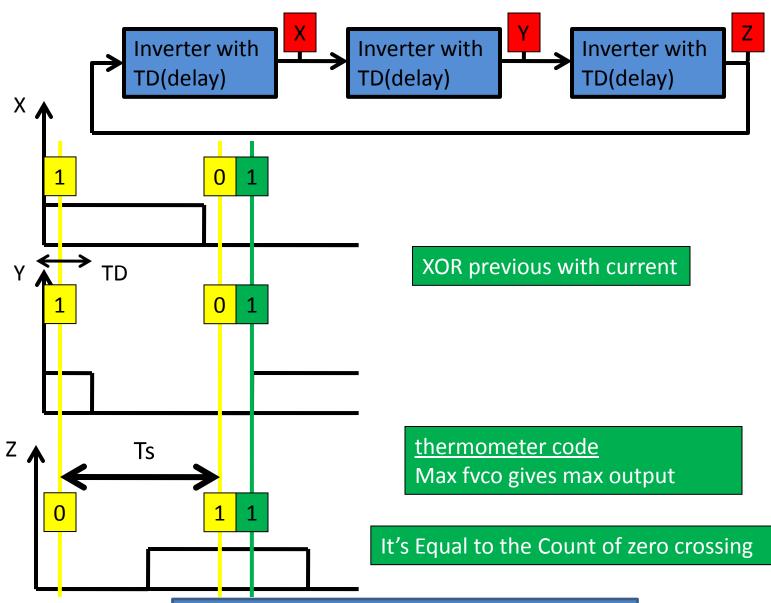

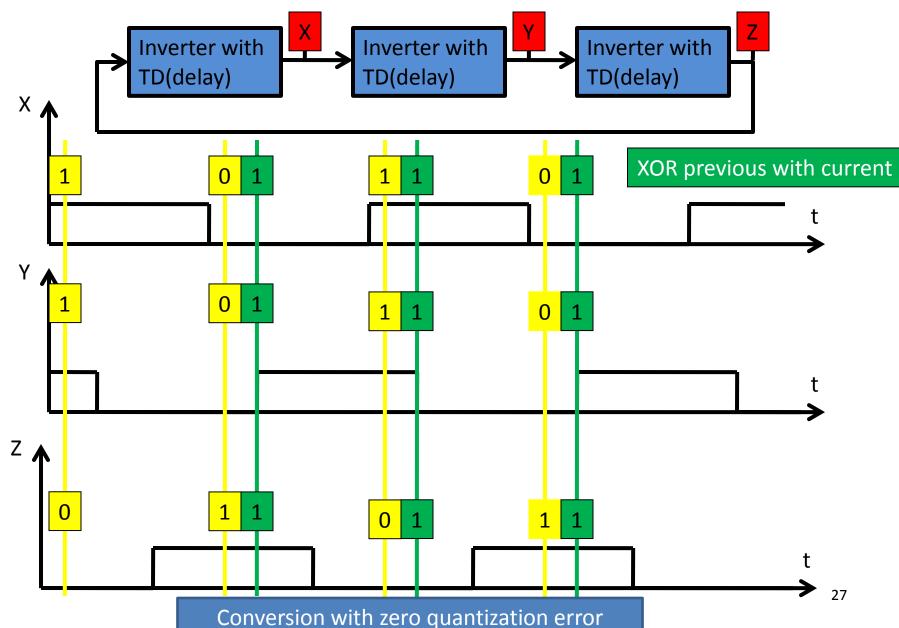

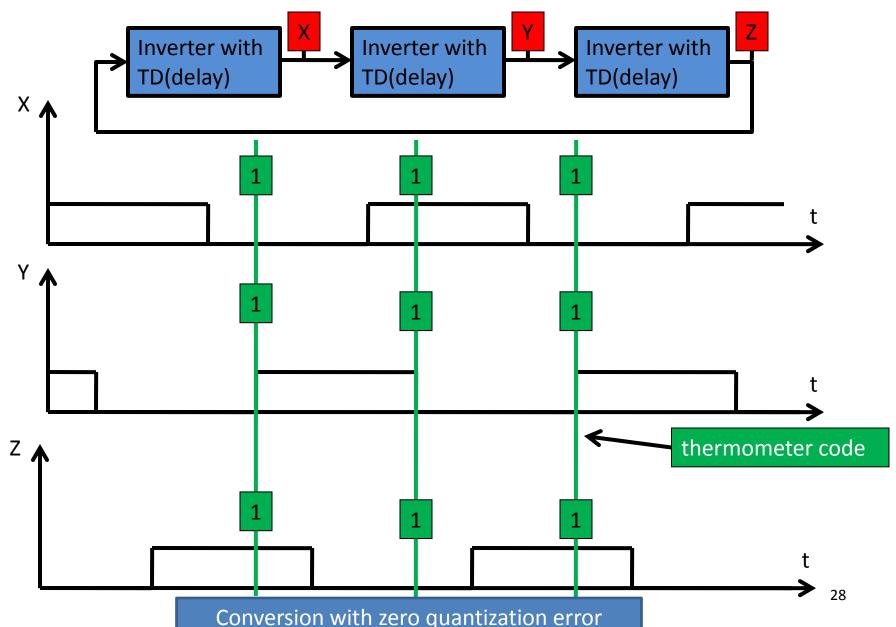

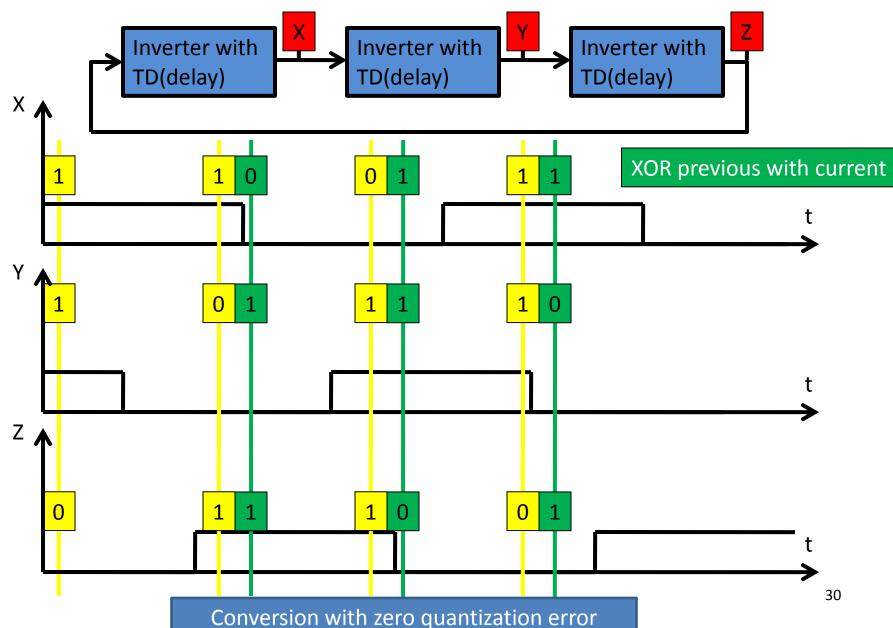

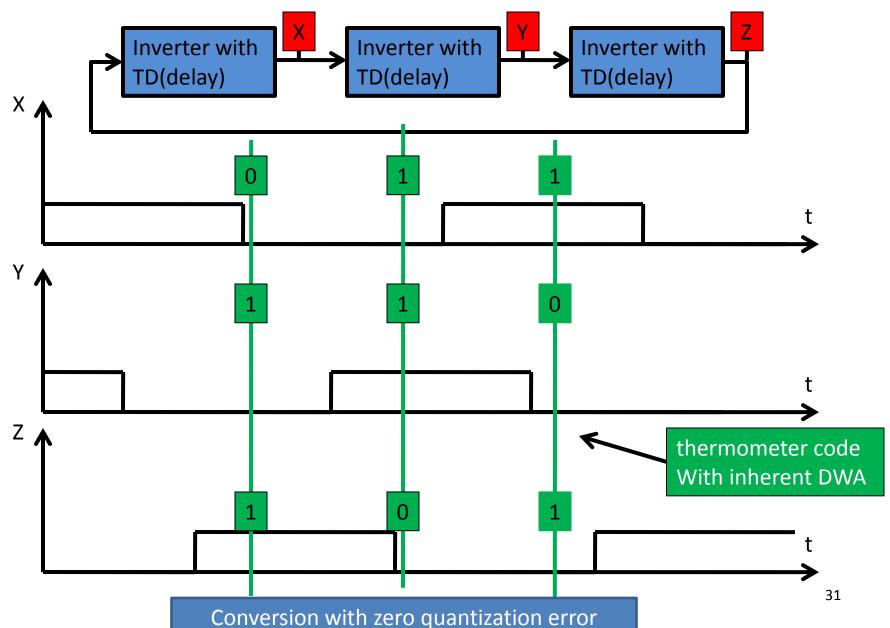

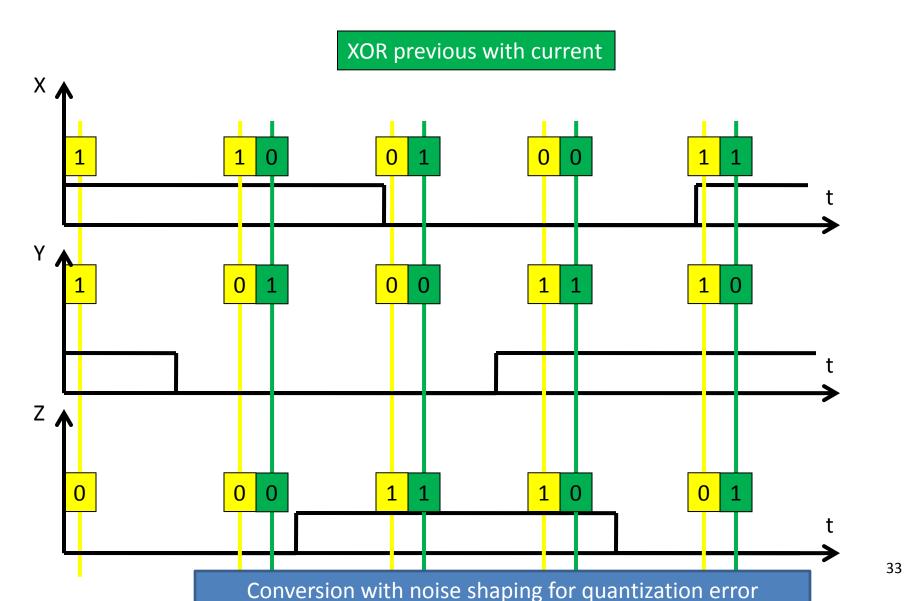

## **3c)**Quantizer Efficient implementaion

Eliminating the Counters reset problem

<u>Frequency Detection</u> Number of inverters switching state between two sampling instances is a count of the zero crossings during this time

1 1 0 0 0 0 1 1 1 5 transitions detected by XOR

## VCO-based Quantizer toggling

2-bit Flash Quantizer

0

1

3

-1 to -0.5

-0.5 to 0

0 to 0.5

0.5 to 1

o/p code

₽ime(sec)

#### 2-bit VCO Quantizer

| Vtune | Fvco | o/p(code) |

|-------|------|-----------|

| -1    | 0    | 0         |

| -1/3  | Fs/6 | 1         |

| 1/3   | Fs/3 | 2         |

| 1     | Fs/2 | 3         |

#### Frequencies (k\*fs/2m) have zero quantization error

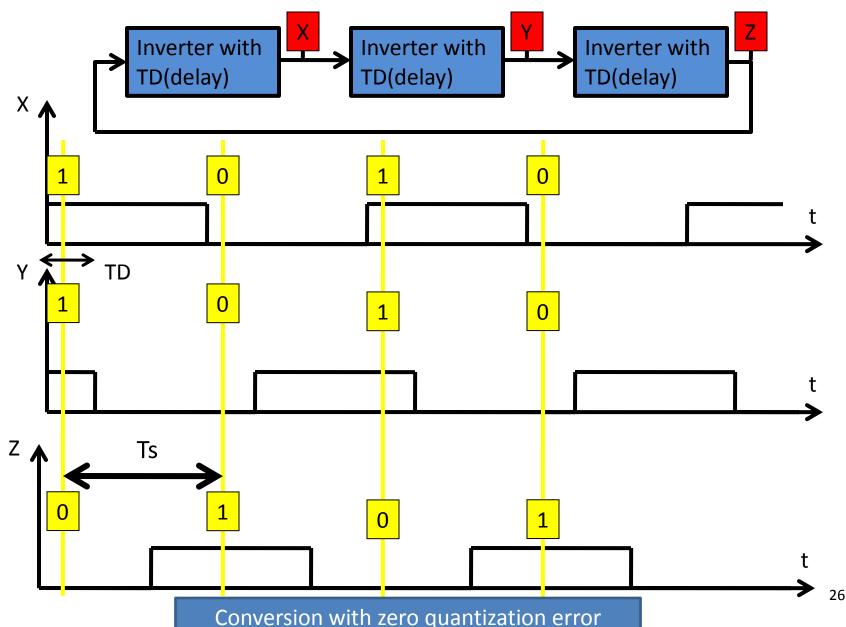

#### Ex1:Quantizing Vtune=1V (fvco=fs/2)

Conversion with zero quantization error

#### Ex1:Quantizing Vtune=1V (fvco=fs/2)

Conversion with zero quantization error

#### Ex1:Quantizing Vtune=1V (fvco=fs/2)

#### Ex1:Quantizing Vtune=1V (fvco=fs/2)

#### Ex1:Quantizing Vtune=1V (fvco=fs/2)

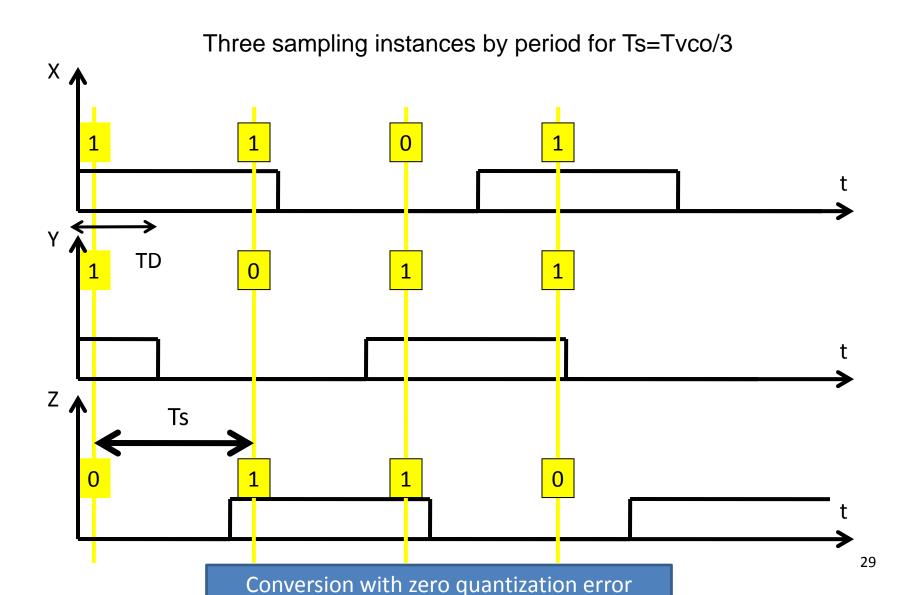

#### Ex2:Quantizing Vtune=1/3V (fvco=fs/3)

#### Ex2:Quantizing Vtune=1/3V (fvco=fs/3)

#### Ex2:Quantizing Vtune=1/3V (fvco=fs/3)

32

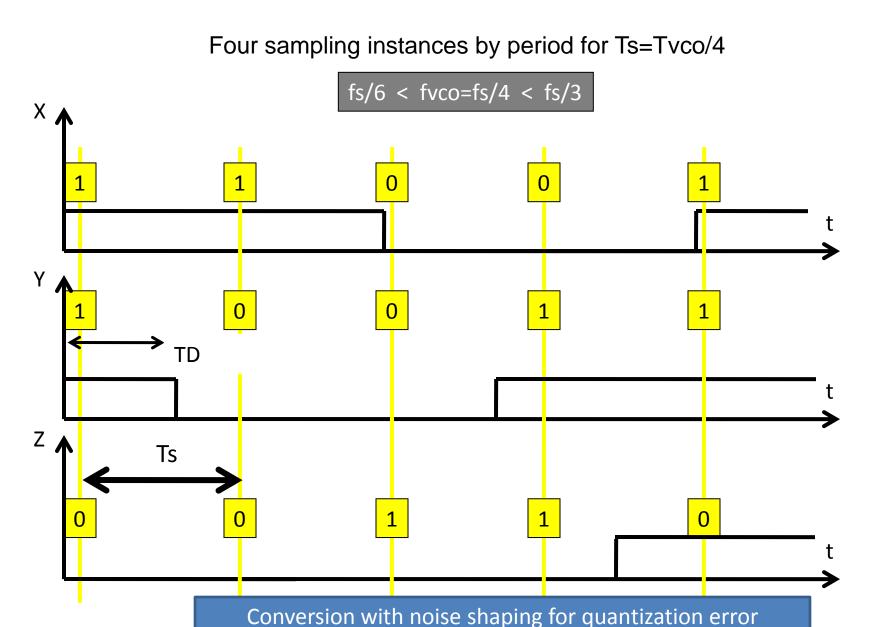

#### Ex3:Quantizing Vtune=1/4V (fvco=fs/4)

#### Ex3:Quantizing Vtune=1/4V (fvco=fs/4)

#### Ex3:Quantizing Vtune=1/4V (fvco=fs/4)

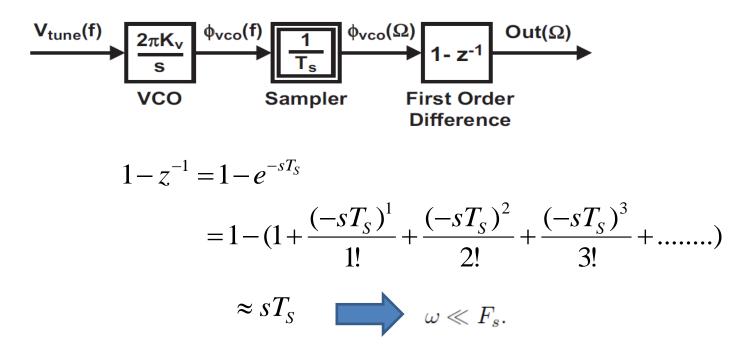

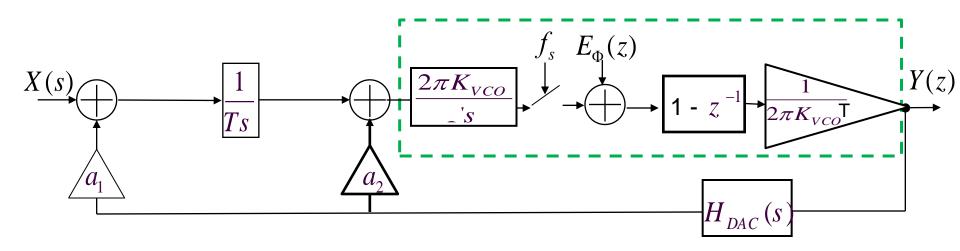

#### VCO-based quantizer Model

### VCO-based quantizer Model validity

DT differentiation may be approximated as the inverse of the CT integration Only for low frequencies with respect to Fs

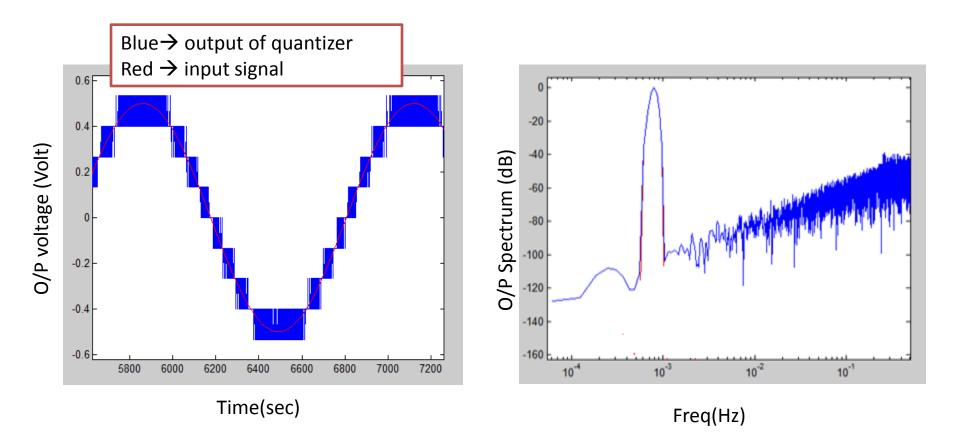

#### VCO-based quantizer (4-bit)simulation

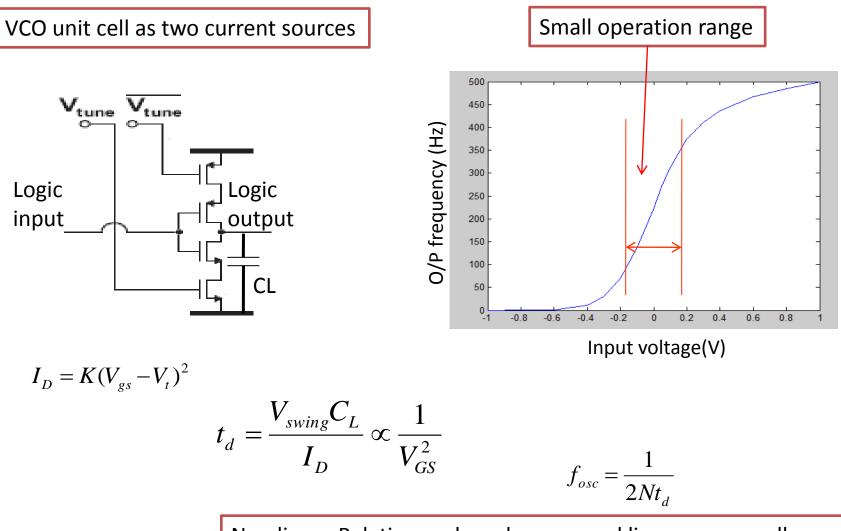

### VCO-based quantizer Circuit drawbacks

Non linear Relation and can be assumed linear on a small range

### VCO-based quantizer Circuit drawbacks

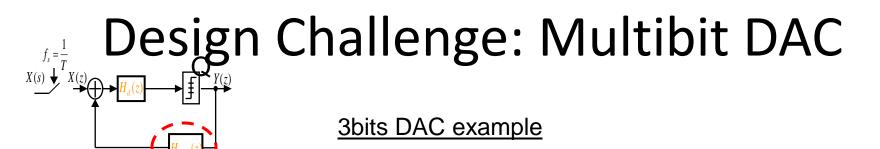

#### Multibit quantization

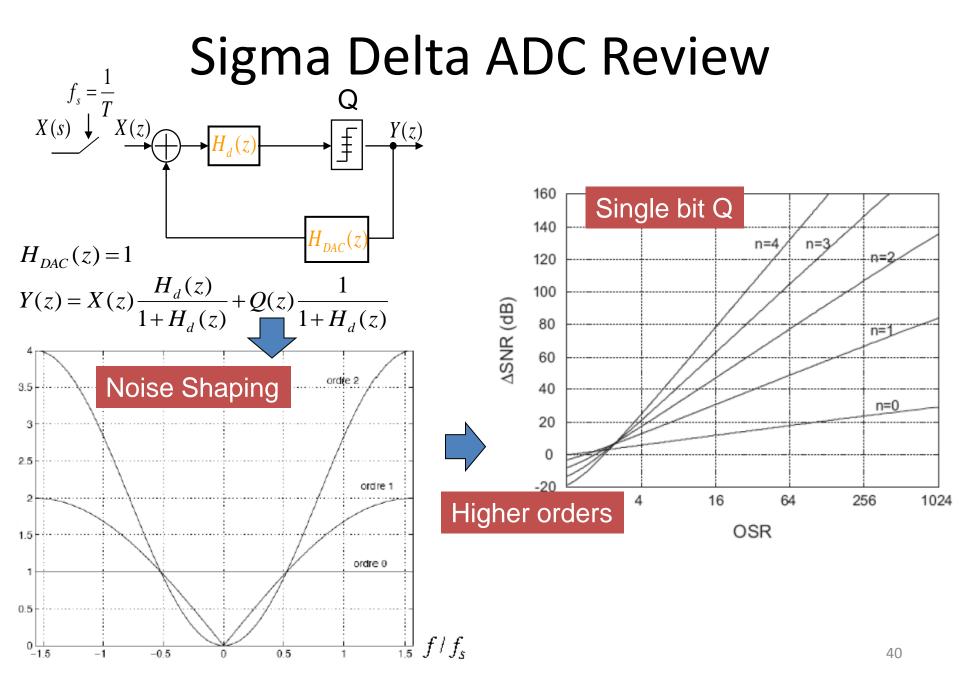

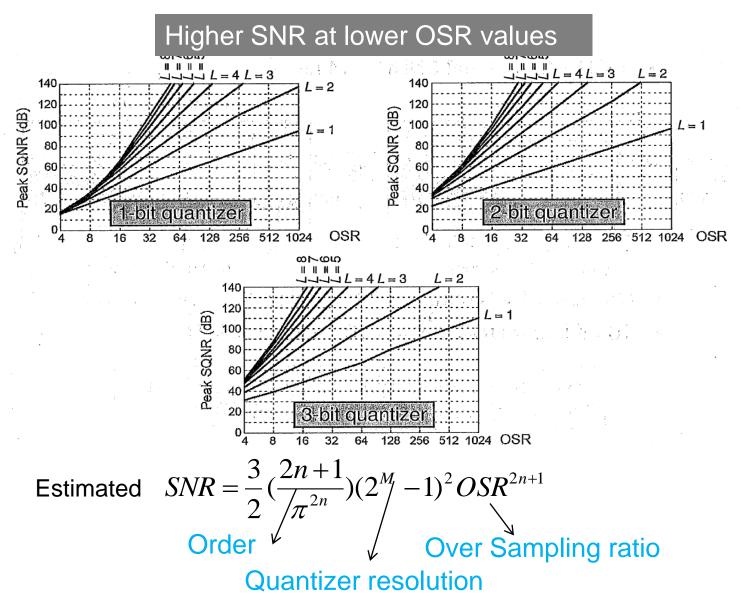

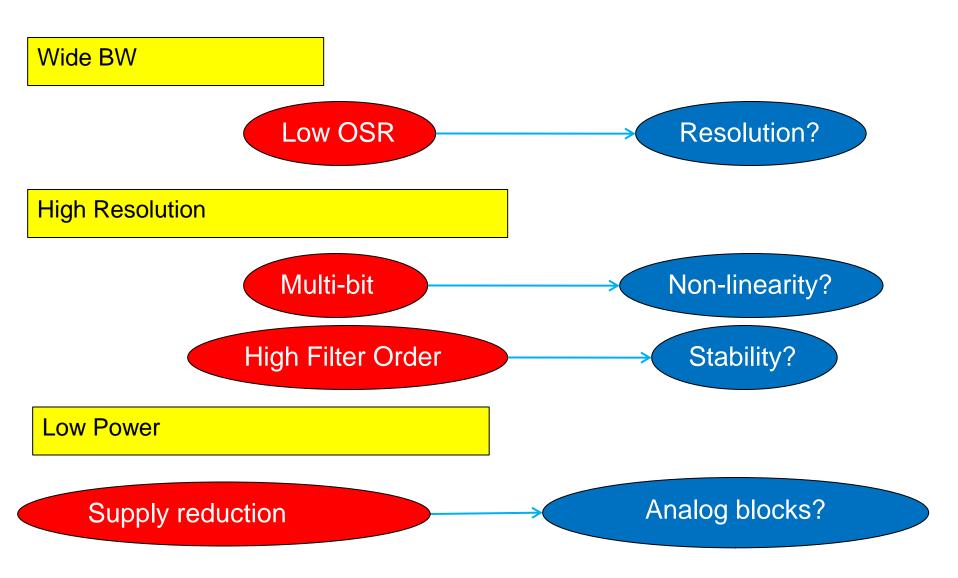

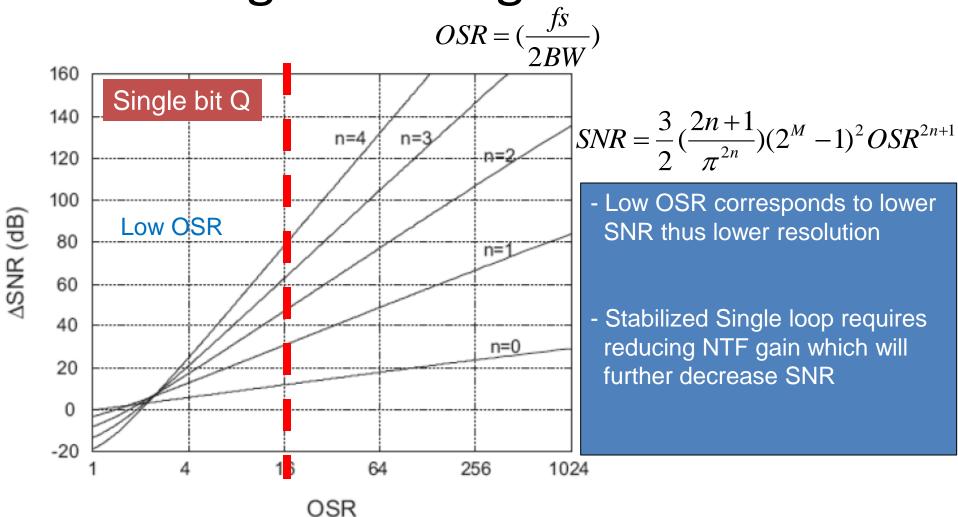

# Sigma Delta Design challenges

#### Design Challenges: Low OSR

DWA\*: Data weighted averaging <sup>44</sup>

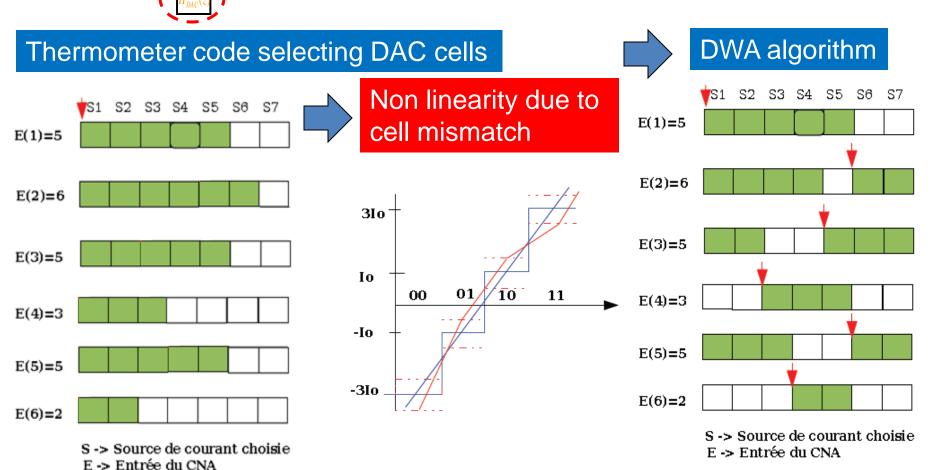

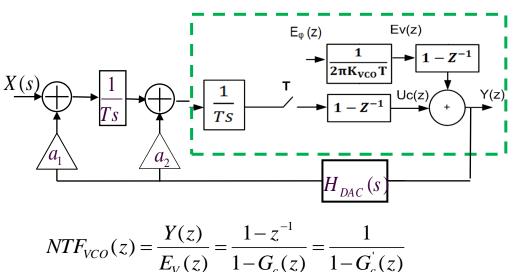

#### Second order SDM with VCO-based Quantizer

- Time Domain Quantization: Low Vdd (deep submicron) compatible

- No Comparators meta-stability, offsets and delay problems

- Inherent DWA without a dedicated circuit

- Saves an integrator (Mostly digitlal implementation)

# SDM with VCO quantizer design(1)

Exploit the 1<sup>st</sup> order noise shaping in the quantizer.

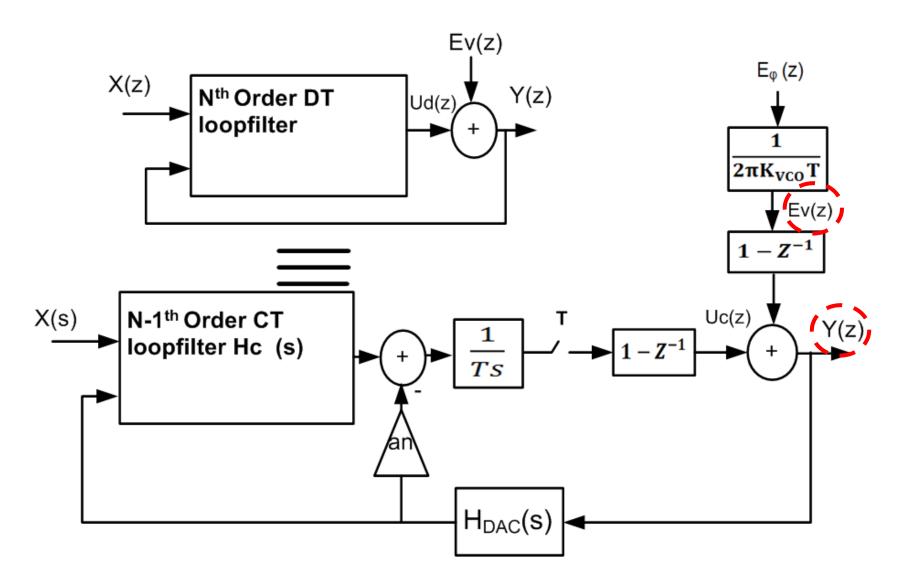

Transformation from Nth order DT to (N-1)th order CT with VCO quantizer

System Level Design

- 1) Get DT  $\Delta\Sigma$  coefficients for Nth order Modulator (Schreier toolbox)

- 2) Get NTFd(z) and Gd(z) of the DT modulator

- 3) Get NTFc(z) and the corresponding loopgain Gc(z) of the CT modulator

- 4) Compare the two similar z orders in both NTF functions and to obtain the CT coefficients

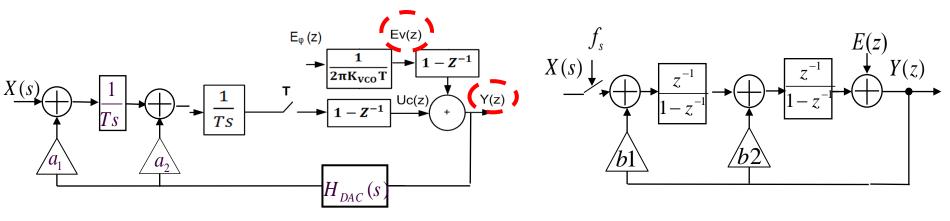

# SDM with VCO quantizer design(2)

# SDM with VCO quantizer design(3)

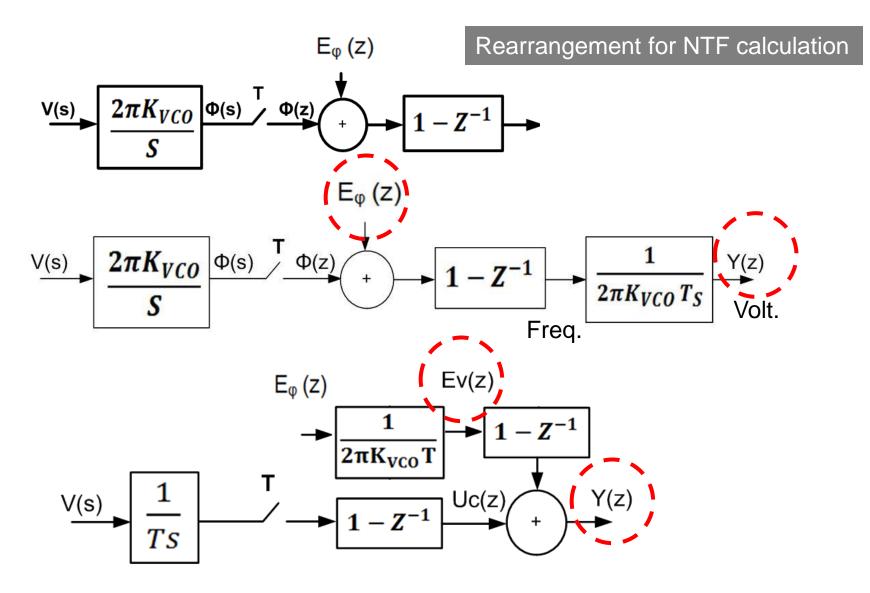

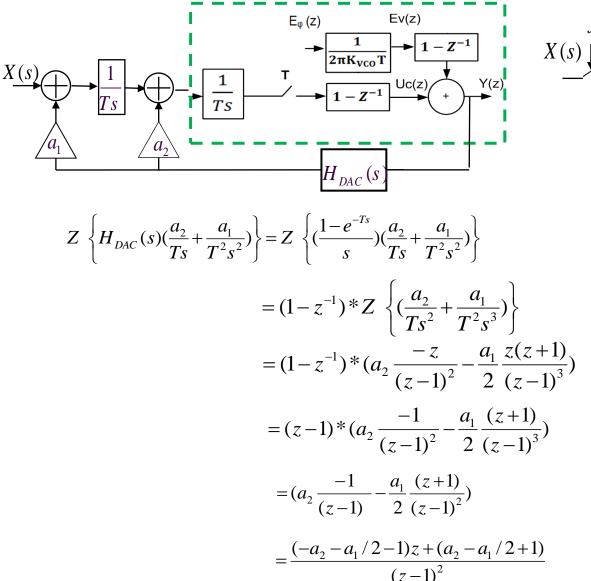

#### SDM with VCO quantizer design(4)

$$NTF_{VCO}(z) = \frac{Y(z)}{E_V(z)} = \frac{1 - z^{-1}}{1 - G_c(z)} = \frac{1}{1 - G_c'(z)}$$

$$G_{c}'(z) = \frac{-z^{-1}}{1-z^{-1}} - Z \left\{ H_{DAC}(s) H_{C}(s) \right\}$$

$$Z \left\{ H_{DAC}(s)(\frac{a_2}{Ts} + \frac{a_1}{T^2s^2}) \right\} = Z \left\{ (\frac{1 - e^{-Ts}}{s})(\frac{a_2}{Ts} + \frac{a_1}{T^2s^2}) \right\}$$

#### SDM with VCO quantizer design(4)

### SDM with VCO quantizer design(4)

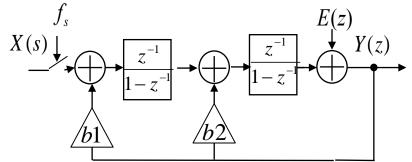

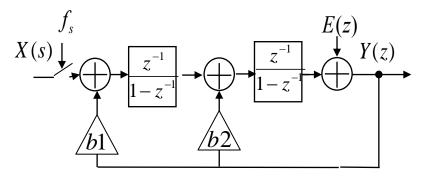

$$NTF_{D}(z) = \frac{Y(z)}{E(z)} = \frac{1}{1 - G_{d}(z)}$$

$$G'_{c}(z) = \frac{(-a_{2} - a_{1}/2 - 1)z + (a_{2} - a_{1}/2 + 1)}{(z - 1)^{2}}$$

$$G_d(z) = \frac{-(b_2)z + b_2 - b_1}{(z-1)^2}$$

$$-b_{2} = -a_{0} - \frac{a_{1}}{2} - 1$$

$$b_{2} - b_{1} = a_{2} - \frac{a_{1}}{2} + 1$$

$$b_{1} = a_{1}$$

$$b_{2} - \frac{b_{1}}{2} - 1 = a_{2}$$

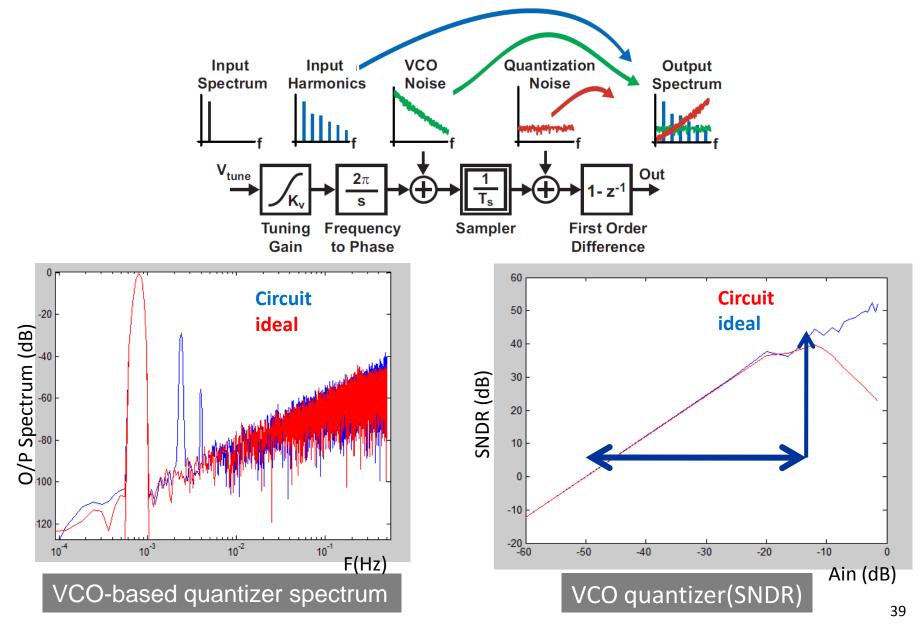

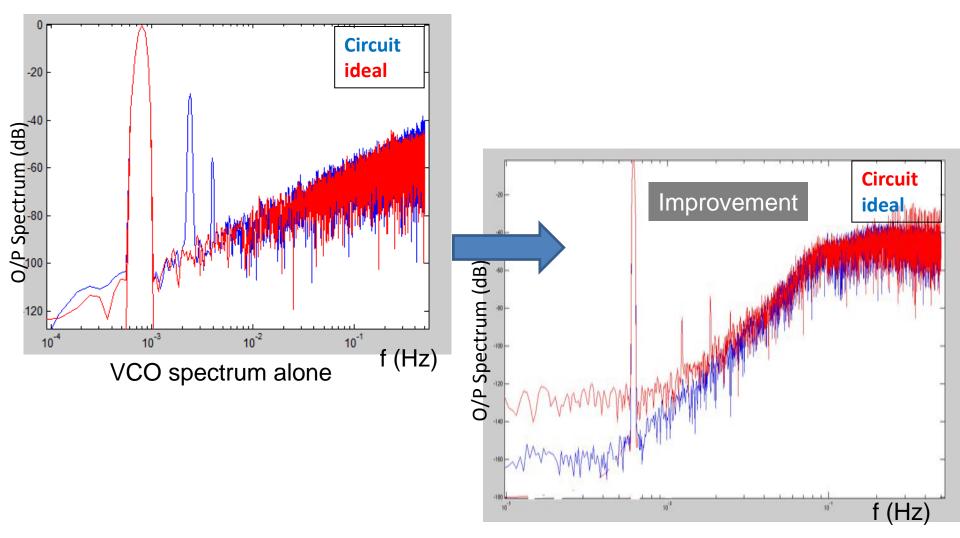

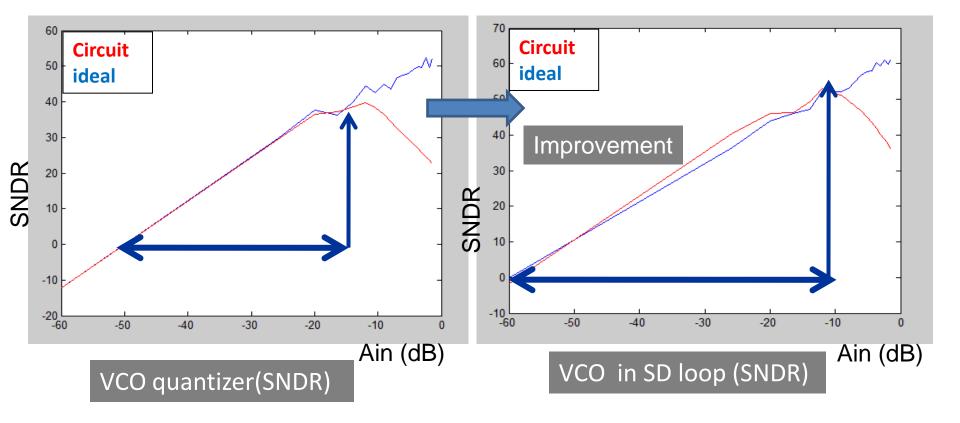

### Non ideal VCO-based quantizer in SD

VCO spectrum in SD loop

### Non ideal VCO-based quantizer in SD

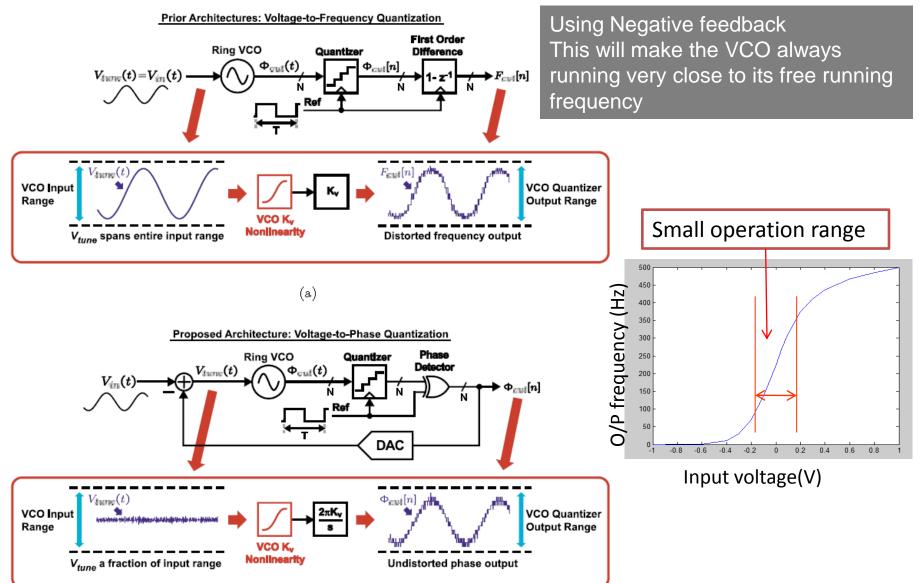

### Linearization through feedback

# Summary & Conclusion

- TDC are potential candidates for modern wide band ADC

- They achieve good resolution and BW efficiently (low power)

- They are compatible with technology scaling thus allowing further efficency in terms of power and area

- Using TDC techniques in ADC need analog to time conversion which is usually non-linear.

- VCO-based quantizer has an important noise shaping property

- The use of VCO-based quantizer as a multi-bit quantizer in SDM decreases the non-linearity due to the SDM loop filter gain.

- Further suppression of non-linearities is possible using Negative Feedback

#### References

- M. Z. Straayer, M. H. Perrott, "A 12-Bit, 10-MHz Bandwidth, Continuous-Time ADC With a 5-Bit, 950-MS/s VCO-Based Quantizer," *IEEE JSSC*, vol. 43, NO. 4, pp.805-814, April 2008

- M. Z. Straayer, "Noise Shaping Techniques for Analog and Time to Digital Converters Using Voltage Controlled Oscillators", *PhD thesis*, *MIT*, June.2008

- H. Aboushady and M.-M. Louerat, "Systematic approach for discrete-time to continuous-time transformation of modulators," *in Proc. IEEE International Symposium on Circuits and Systems, (ISCAS'02)*, vol. 4, 2002, pp. IV–229–IV–232

- H. Aboushady, "Conception En Vue De La Realization De Convertisseurs Analogique- Numerique ΣΔ Temps-Continu Mode courant", Phd thesis, UPMC, Lip6, Jan. 2002.

- M. J. Park, "A 4th Order Continuous-Time ΔΣ ADC with VCO-Based Integrator and Quantizer", *PhD thesis*, *MIT*, Feb.2009

- T. E. Rahkone, J. T. Kostamovaara, "The Use of Stabilized CMOS Delay Lines for the Digitization of Short Time Intervals", *IEEE JSSC*, vol. 28, no. 8, Aug. 1993

- J.Kim, S. Cho, "A time-based analog-to-digital converter using a multi-phase voltage controlled oscillator," *ISCAS 2006.*