## A Designer Centric Analog Synthesis Flow

## Farakh JAVID, Stéphanie YOUSSEF, Ramy ISKANDER, Marie-Minerve LOUËRAT

LIP6 Laboratory, University Pierre & Marie Curie, Paris, France

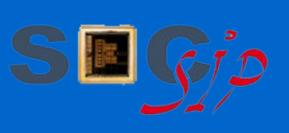

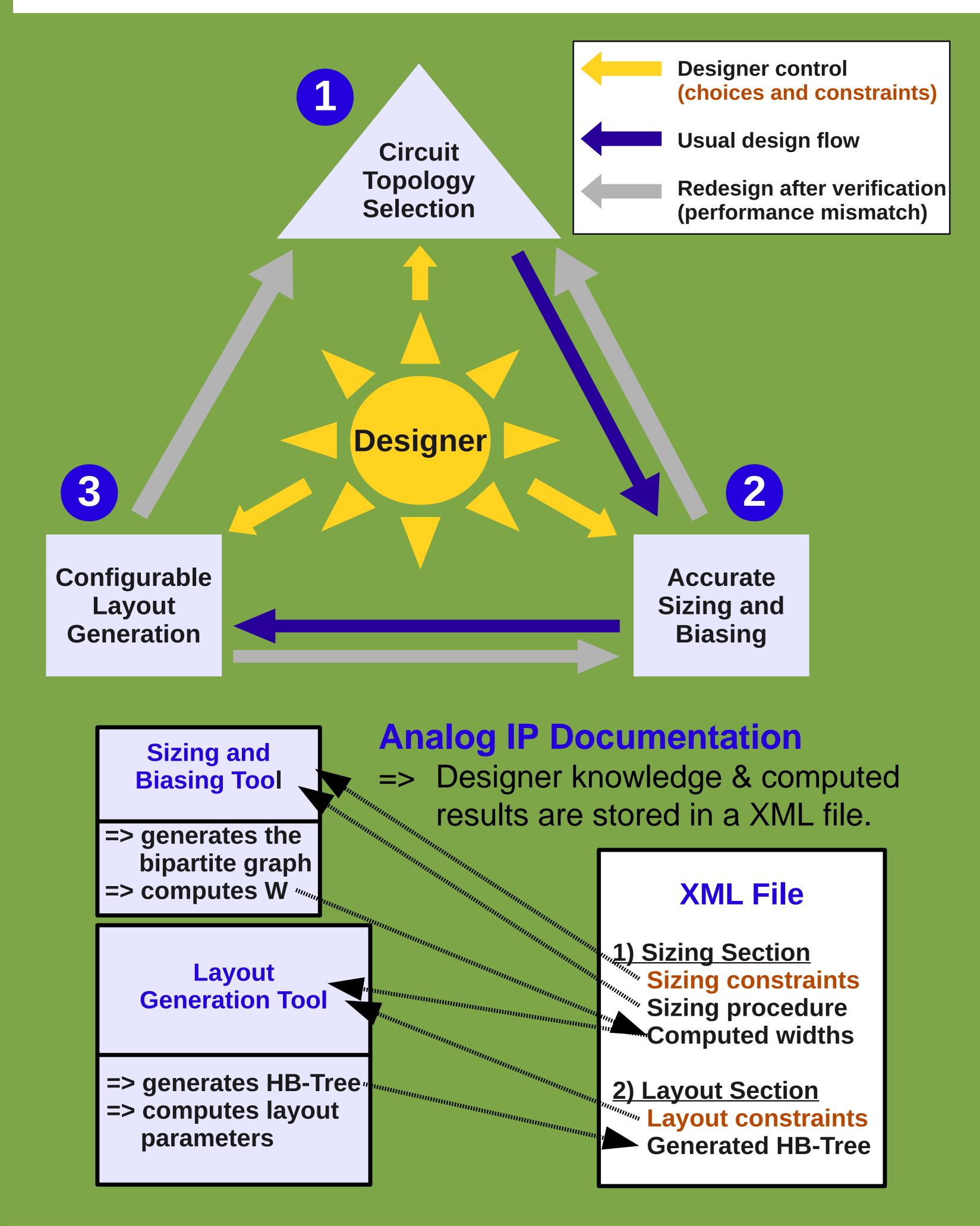

This poster presents a *designer centric analog synthesis flow* that is fully controlled by the designer and offers an intuitive design approach. The designer knowledge to conceive an analog IP is the key element of the synthesis flow, it is taken into account to automatically generate the analog IP design procedure and physical view. Thus both consistency and accuracy of the final design are ensured. The presented design flow bridges the gap between the two traditional approaches related to analog design automation, namely the simulation-based and the knowledge-based approaches, to profit from both approach advantages. The designer centric analog synthesis flow is composed of an accurate sizing tool and a configurable layout generation tool. Both tools are used to synthesize a fully differential transconductor.

## **Accurate Sizing and Biasing Tool**

- Based on the hierarchical sizing and biasing methodology

- => sizing procedure generation according to the designer knowledge

- Sizing & biasing operators with standard simulator interface

- => accurate sizing with standard device models (BSIM3v3, BSIM4, PSP, EKV)

- Bipartite graph

- => represents the sizing procedure

- => evaluated from top to bottom to compute transistor sizes

## **Configurable Layout Generation Tool**

- Based on Python language

- => concise code to describe complex layout

- Stack object

- => represents the folded transistor

- Routing methodologies

- HB-Tree

- => represents a compact placement

OPVG(VEG,VE

Vg Vth W

**Bipartite Graph**