| Version 9 (modified by , 14 years ago) (diff) |

|---|

TP1 : Plate forme de simulation + Synthèse

Introduction

Le but des 4 TPs est d'effectuer la conception physique d'un Mips R3000 pipeline.

Vous devez appliquer la méthodologie vue dans les Tps de Tools.

Vous avez à disposition une archive contenant l'ensemble des fichiers nécessaires aux TPs. Pour décompresser cette archive, utilisez la commande suivante :

> tar xjvf sources.tar.bz2

Vous obtenez un répertoire sources contenant lui même six autres répertoires :

- asm : contient les programmes assembleurs qui seront exécutés sur la carte contenant le MIPS pour vérifier son fonctionnement.

- design : contient les descriptions comportementales ou structurelles des différentes parties du MIPS, que vous devez utiliser pour écrire la description structurelle de l'ensemble du circuit (en python).

- mips : contient un fichier comportemental décrivant le mips dans lequel le découpage chemin de données / partie contrôle n'est pas effectué.

- misc : contient les fichiers utiles à la création de l'environnement de test du MIPS.

- ram : contient les fichiers décrivant le fonctionnement de la ram.

- test_mips : contient les fichiers de test.

Le répertoire test_mips contient un script shell nommé test.sh vous permettant de lancer l'intégralité des tests sur votre MIPS. Vous pouvez tester deux mises en oeuvre du MIPS à l'aide des commandes suivantes :

> ./test.sh v1

permet de lancer tous les tests en utilisant la description comportementale du mips (fichier dans le répertoire mips).

> ./test.sh v2

permet de tester le découpage des parties contrôle et chemin de données (en comportemental) instanciées par une hiérarchie structurelle du coeur et du circuit complet (avec plots) (fichiers dans le répertoire design).

Vous avez également à disposition la commande :

> ./test.sh v3

qui permettra de lancer tous les tests en utilisant tous les fichiers .vst générés une fois votre MIPS terminé.

Remarques :

- Avant de pouvoir utiliser le script test.sh pour la première fois, il faut aller dans le répertoire asm et lancer le script ASM.csh

- Notez bien que pour utiliser la seconde commande présentée vous devez au préalable avoir généré les fichiers mips_r3000_1m.vst et mips_r3000_1m_core.vst à l'aide du script gen_mips.py et du Makefile situés dans le répertoire design.

- Notez également vous pouvez tout à fait compléter ce script de façon à tester des versions "intermédiaires", la partie controle en .vst et le chemin de données en .vbe par exemple pour tester l'étape d'aujourd'hui : la synthèse de la partie controle.

/!\ ERRATUM /!\ : Veuillez récupérer le fichier SIM.csh et remplacer le fichier de même nom dans les sources fournies dans le répertoire test_mips.

1 Plate forme de simulation

1.1 Les programmes assembleurs pour la plate forme de simulation

Lors de la conception du processeur, à chaque étape, il faut vérifier que le résultat obtenu est conforme aux spécifications du processeur. Une des vérifications qui doit être appliquée systématiquement est la vérification fonctionnelle. Elle consiste à s'assurer que le circuit obtenu à cette étape de conception est toujours conforme à l'architecture du Mips. Bien évidemment, cette vérification ne peut être que partielle.

Pour vous aider dans cette tâche, un ensemble de programmes de test est fourni. A priori, on peut imaginer qu'un programme de test consiste simplement à exécuter une instruction. Puis, il suffit de vérifier à travers les patterns en affichant la valeur des registres visibles que l'instruction a été correctement exécutée. Toutefois cette méthode est très pénible et nécessite l'intervention du concepteur pour valider la bonne exécution de chacune des instructions.

Nous vous proposons une autre méthode. Les programmes assembleur fournis sont écrits de telle manière qu'ils vérifient le résultat de l'exécution de l'instruction objet du test à travers une suite d'instructions. A l'issue de ce test, le programme se branche à deux adresses différentes en fonction du résultat du test. Dans chacune de ces branches une valeur différente est écrite en mémoire. Un dispositif particulier sur la plateforme de simulation surveille les valeurs écrites en mémoire. Lorsque ce dispositif voit l'écriture de la valeur qui signale l'exécution correcte du programme, il arrête la simulation et affiche un message qui indique que l'exécution s'est déroulée correctement. A l'inverse l'écriture de la valeur qui dénote un dysfonctionnement déclenche l'arrêt de la simulation et un message indiquant la mauvaise exécution du programme est affiché.

1.2 Exemple

###----------------------------------------------------------------###

# file : add000.u #

# date : Mar 26 1996 #

# descr. : functional test for Mips R3000 #

###----------------------------------------------------------------###

.text

###--------------------------------------------------------###

# signed addition #

###--------------------------------------------------------###

good_val .equ 0x01

bad_val .equ 0x02

sim_addr .equ user_cntl_begin

val1 .equ 0x0000000a

val2 .equ 0x00000002

init:

li r1 , val1

li r2 , val2

add r3 , r2 , r1

li r5 , (val1 + val2)

beq r5 , r3 , good

nop

j bad

nop

###--------------------------------------------------------###

# signaling good / bad #

###--------------------------------------------------------###

good:

li r1 , sim_addr

addiu r2 , r0 , good_val

j end_loop

nop

bad:

li r1 , sim_addr

addiu r2 , r0 , bad_val

j end_loop

nop

end_loop:

sb r2 , 0(r1 )

j end_loop

nop

.end

1.3 L'assemblage des programme

L'outil assembleur permet de générer une image mémoire à partir de fichiers écrits en assembleur. Cet outil prend en entrée une liste de fichiers assembleur et le fichier ldscript et génère une image mémoire dans un fichier de sortie.

> asm -set noreorder -ld <ldscript> -mips1 -o <fichier_image> <fichier_ass> …

1.4 La plateforme de simulation pour le processeur MIPS

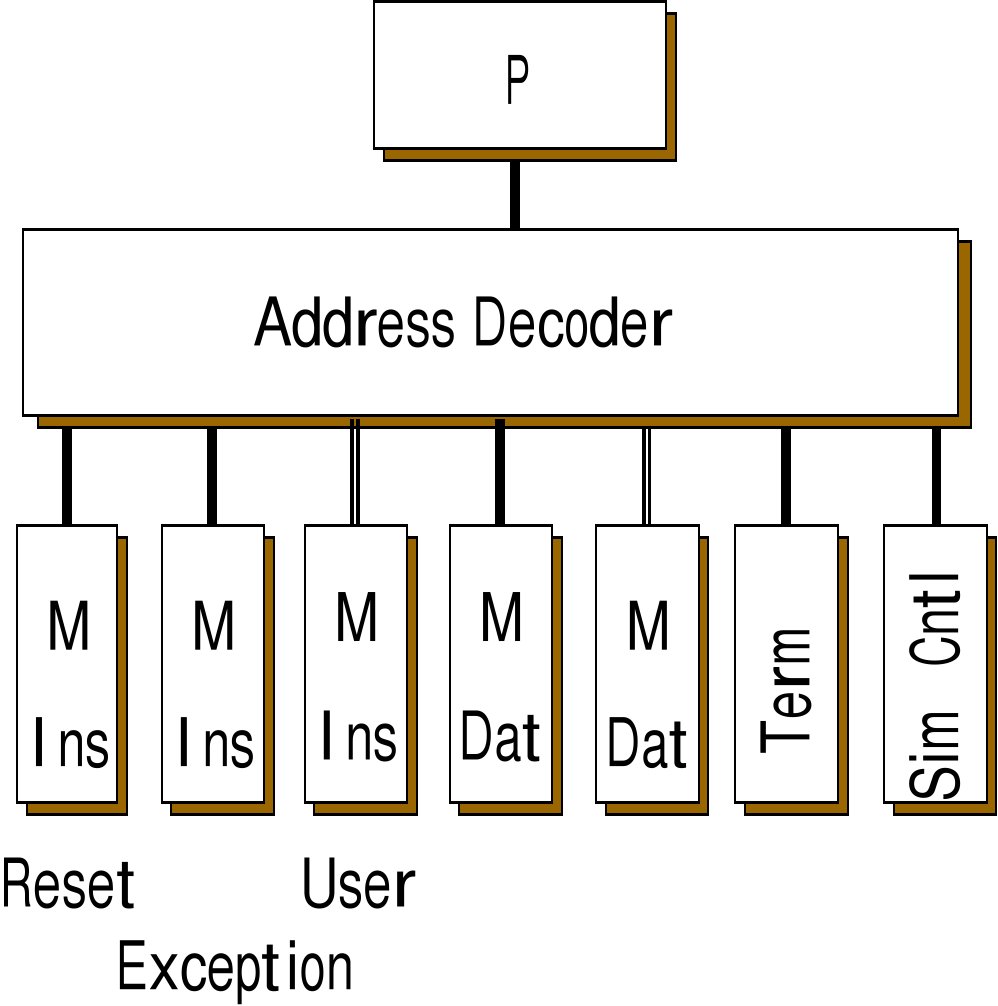

Une plateforme de simulation construite autour d'un processeur MIPS permet de simuler l'exécution d'un programme assembleur. Outre le processeur Mips, cette plateforme comporte des bancs mémoires pour les instructions et les données, un terminal d'affichage, un dispositif de détection de fin de simulation et un décodeur d'adresses. Le décodeur d'adresses sélectionne, en fonction de l'adresse émise par le processeur, le banc mémoire qui doit répondre au processeur ou bien le terminal d'affichage ou encore le dispositif qui arrête la simulation.

Sur cette plateforme les bancs mémoires sont initialisés à partir de l'image mémoire obtenue par l'assemblage d'un programme assembleur. Cette image doit se trouver dans le fichier ram.ini et ce fichier doit être placé dans le répertoire où la simulation est lancée.

Le fichier de patterns nécessaire à la simulation est très simple. En pratique, cette plateforme n'a que deux entrées : l'horloge et le signal de reset. Pendant le premier cycle de simulation, le signal reset est actif (ce signal est actif à l'état bas) puis, il reste inactif pendant le reste de la simulation. L'horloge est un signal périodique qui passe successivement de 0 à 1 et de 1 à 0.

2 Synthèse de la partie controle

Le but est ici d'utiliser les différents outils de synthèse à votre disposition pour générer la vue structurelle de la partie controle à partir de la description comportementale fournie. Vous testerez les options des différents outils pour avoir une netlist optimisée.

Vous écrirez un Makefile qui sera à compléter au fur et à mesure des TPs.

Attachments (3)

- simu.jpg (72.6 KB) - added by 14 years ago.

- sources.tar.bz2 (84.3 KB) - added by 14 years ago.

- SIM.csh (1.2 KB) - added by 14 years ago.

Download all attachments as: .zip