| Acronym of the proposal             | COACH                                                    |  |  |  |  |

|-------------------------------------|----------------------------------------------------------|--|--|--|--|

| Title of the proposal in French     | Conception d'Architecture sur FPGA par Compilation et    |  |  |  |  |

|                                     | $\operatorname{synt}\mathbf{H}$ èse                      |  |  |  |  |

| Title of the proposal in<br>English | Architecture Design on FPGA by Compilation and Synthesis |  |  |  |  |

| Theme                               | ■ 1 ● 2 ● 3 □ 4 ● 5<br>•: secondary theme                |  |  |  |  |

|                                     | Experimental Development                                 |  |  |  |  |

| Type of research                    | Industrial Research                                      |  |  |  |  |

|                                     | $\Box$ Basic Research                                    |  |  |  |  |

| Type of scientific project          | Platform                                                 |  |  |  |  |

| Total requested<br>funding          | 1195931 € Project Duration $36 \text{ months}$           |  |  |  |  |

# Contents

| 1 | Exe                                     | cutive summary                                                                                                                                                                                                                                                                                                                                                                                                | <b>2</b>                                                                                                                                                   |

|---|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Con<br>2.1<br>2.2                       | text and relevance to the call<br>Economic and societal issues                                                                                                                                                                                                                                                                                                                                                | $egin{array}{c} 4 \\ 6 \\ 7 \end{array}$                                                                                                                   |

| 3 | <b>Scie</b> 3.1<br>3.2                  | Intific and technical DescriptionState of the Art3.1.1High Performance Computing3.1.2System Synthesis3.1.3High Level Synthesis3.1.4Application Specific Instruction Processors3.1.5Automatic ParallelizationS & T objectives, progress beyond the state of the art                                                                                                                                            | <ol> <li>9</li> <li>9</li> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>12</li> </ol>                                                               |

| 4 | Scie<br>4.1<br>4.2<br>4.3               | Intific and technical objectives / project descriptionScientific Programme, Project structureProject managementObscription of the tasks4.3.1Task 1: Project management4.3.2Task 2: Backbone infrastructure4.3.3Task 3: System generation4.3.4Task 4: HAS front-end4.3.5Task 5: HAS back-end4.3.6Task 6: PC/FPGA communication middleware4.3.8Task 8: DisseminationTasks schedule, deliverables and milestones | <ol> <li>14</li> <li>14</li> <li>17</li> <li>18</li> <li>19</li> <li>21</li> <li>23</li> <li>25</li> <li>26</li> <li>28</li> <li>31</li> <li>32</li> </ol> |

| 5 | <b>Diss</b><br>5.1<br>5.2<br>5.3<br>5.4 | semination and exploitation of results. Management of intellectual property         Dissemination         Exploitation of results         Indusrial Interest in COACH         Management of Intellectual Property                                                                                                                                                                                             | <b>35</b><br>35<br>37<br>37<br>39                                                                                                                          |

| ADDATE INTERNAL DELA RECERCIÓN |  |

|--------------------------------|--|

|                                |  |

| AINI                           |  |

| TTTT                           |  |

|                                |  |

| 6            | Cor  | nsortium Description                                        | 39         |  |  |  |  |  |  |  |  |  |

|--------------|------|-------------------------------------------------------------|------------|--|--|--|--|--|--|--|--|--|

|              | 6.1  | Partners description & relevance, complementarity           | 39         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.1 INRIA/CAIRN                                           | 39         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.2 ENS Lyon/LIP/Compsys                                  | 39         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.3 TIMA                                                  | 39         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.4 LAB-STICC                                             | 40         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.5 LIP6                                                  | 40         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.6 XILINX                                                | 41         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.7 BULL                                                  | 41         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.8 THALES                                                | 42         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.9 FLEXRAS                                               | 42         |  |  |  |  |  |  |  |  |  |

|              |      | 6.1.10 NAVTEL-SYSTEM                                        | 42         |  |  |  |  |  |  |  |  |  |

|              | 6.2  | Relevant experience of the project coordinator              | 43         |  |  |  |  |  |  |  |  |  |

|              |      |                                                             |            |  |  |  |  |  |  |  |  |  |

| 7            |      | entific justification for the mobilisation of the resources | 43         |  |  |  |  |  |  |  |  |  |

|              | 7.1  | Partner 1: INRIA/CAIRN                                      | 43         |  |  |  |  |  |  |  |  |  |

|              | 7.2  | Partner 2: ENS Lyon/LIP                                     | 44         |  |  |  |  |  |  |  |  |  |

|              | 7.3  | Partner 3: TIMA                                             | 45         |  |  |  |  |  |  |  |  |  |

|              | 7.4  | Partner 4: LAB-STICC                                        | $45 \\ 46$ |  |  |  |  |  |  |  |  |  |

|              | 7.5  | Partner 5: LIP6                                             |            |  |  |  |  |  |  |  |  |  |

|              | 7.6  | Partner 6: XILINX                                           | 47         |  |  |  |  |  |  |  |  |  |

|              | 7.7  | Partner 7: BULL                                             | 47         |  |  |  |  |  |  |  |  |  |

|              | 7.8  | Partner 8: THALES                                           | 48         |  |  |  |  |  |  |  |  |  |

|              | 7.9  | Partner 9: FLEXRAS                                          | 48         |  |  |  |  |  |  |  |  |  |

|              | 7.10 | Partner 10: NAVTEL-SYSTEM                                   | 49         |  |  |  |  |  |  |  |  |  |

| Δ            | Bib  | liography                                                   | 52         |  |  |  |  |  |  |  |  |  |

| 11           | DID  | nography                                                    | 02         |  |  |  |  |  |  |  |  |  |

| $\mathbf{B}$ | Let  | ters of interest                                            | <b>55</b>  |  |  |  |  |  |  |  |  |  |

|              | B.1  | ALTERA Corporation                                          | 55         |  |  |  |  |  |  |  |  |  |

|              | B.2  | ADACSYS                                                     | 57         |  |  |  |  |  |  |  |  |  |

|              | B.3  | MAGILLEM Design Services                                    | 58         |  |  |  |  |  |  |  |  |  |

|              | B.4  | INPIXAL                                                     | 59         |  |  |  |  |  |  |  |  |  |

|              | B.5  | CAMKA System                                                | 60         |  |  |  |  |  |  |  |  |  |

|              | B.6  |                                                             | 61         |  |  |  |  |  |  |  |  |  |

|              | B.7  | ALSIM Simulateur                                            | 62         |  |  |  |  |  |  |  |  |  |

|              | B.8  | SILICOMP-AQL                                                | 63         |  |  |  |  |  |  |  |  |  |

|              | B.9  | ABOUND Logic                                                | 64         |  |  |  |  |  |  |  |  |  |

|              | B.10 | DEADS-ASTRIUM                                               | 65         |  |  |  |  |  |  |  |  |  |

|              |      |                                                             |            |  |  |  |  |  |  |  |  |  |

# 1 Executive summary

The market of digital systems is about 4,600 M\$ today and is estimated to 5,600 M\$ in 2012. However the ever growing applications complexity involves integration of heterogeneous technologies and requires the design of complex Multi-Processors System on Chip (MPSoC).

During the last decade, the design of ASICs (Application Specific Integrated Circuits) appeared to be more and more reserved to high volume markets, because the design and fabrication costs of such components exploded, due to increasing NRE (Non Recurring-Engineering) costs. Fortunately, FPGA (Field Programmable Gate Array) components, such as the Virtex5 family from XILINX or the Stratix4 family from ALTERA, can nowadays implement a complete MPSoC with multiple processors and several dedicated coprocessors for a few Keuros per device. Many applications are initially captured algorithmically in High-Level Languages (HLLs) such as C/C++. This has led to growing interest in tools that can provide an implementation path directly from HLLs to hardware. Thus, Electronic System Level (ESL) design methodologies (Virtual Prototyping, Co-design, High-Level Synthesis...) are now mature and allow the automation of a system-level design flow. Unfortunately, ESL tool development to date has primarily focused on the design of hard-wired devices i.e. ASICs and ASSPs (Application Specific Standard Product). However, the increasing sophistication of FPGAs has accelerated the need for FPGA-based ESL design methodologies. ESL methodologies hold the promise of streamlining the design approach by accepting designs written in C/C++ language and implementing the function straight into FPGA. We believe that coupling FPGA technologies and ESL methodologies will allow both SMEs (Small and Medium Enterprise) and major companies to design innovative devices and to enter new, low and medium volume markets.

The objective of COACH is to provide an integrated design flow, based on the SoCLib infrastructure [8], and optimized for the design of multi-processors digital systems targeting FPGA devices. Such digital systems are generally integrated into one or several chips, and there are two types of applications: They can be embedded (autonomous) applications such as personal digital assistants (PDA), ambiant computing components, or wireless sensor networks (WSN). They can also be extension boards connected to a PC to accelerate a specific computation, as in High-Performance Computing (HPC) or High-Speed Signal Processing (HSSP).

The COACH environment will integrate several hardware and software technologies:

- **Design Space Exploration:** The COACH environment will allow to describe an application as a process network i.e. a set of tasks communicating through FIFO channels. COACH will allow to map the application on a shared-memory, MPSoC architecture. It will permit to easily explore the design space to help the system designer to define the proper hardware/software partitioning of the application. For each point in the design space, metrics such as throughput, latency, power consumption, silicon area, memory allocation and data locality will be provided. These criteria will be evaluated by using the SoCLib virtual prototyping infrastructure and high-level estimation methodologies.

- Hardware Accelerators Synthesis (HAS): COACH will allow the automatic generation of hardware accelerators when required. Hence, High-Level Synthesis (HLS) tools, Application Specific Instruction Processor (ASIP) design environment and source-level transformation tools (loop transformations and memory optimisation) will be provided. This will allow further exploration of the micro-architectural design space. HLS tools are sensitive to the coding style of the input specification and the domain they target (control vs. data dominated). The HLS tools of COACH will support a common language and coding style to avoid re-engineering by the designer.

- **Platform based design:** COACH will handle both ALTERA and XILINX FPGA devices. COACH will define architectural templates that can be customized by adding dedicated coprocessors and ASIPs and by fixing template parameters such as the number of embedded processors, the number of sizes of embedded memory banks or the embedded the operating system. However, the specification of the application will be independent of both the architectural template and the target FPGA device. Basically, the following three architectural templates will be provided:

- 1. A Neutral architectural template based on the SoCLib IP core library and the VCI/OCP communication infrastructure.

- 2. An ALTERA architectural template based on the ALTERA IP core library, the AVALON system bus and the NIOS processor.

- 3. A XILINX architectural template based on the Xilinx IP core library, the PLB system bus and the Microblaze processor.

Hardware/Software communication middleware: COACH will implement an homogeneous HW/SW communication infrastructure and communication APIs (Application Programming Interface), that will be used for communications between software tasks running on embedded processors and dedicated hardware coprocessors.

The COACH design flow will be dedicated to system designers, and will as much as possible hide the hardware characteristics to the end-user.

To reach this ambitious goal, the project will rely on the experience and the complementariness of partners in the following domains: Operating system and communication middleware (TIMA, LIP6), MPSoC architectures (TIMA, LAB-STICC, LIP6), ASIP architectures (INRIA/CAIRN), High Level Synthesis (TIMA, LAB-STICC, LIP6), and compilation (ENS Lyon/LIP).

The COACH project does not start from scratch. It stronly relies on the SoCLib virtual prototyping platform [8] for prototyping, (DSX, component library), operating systems (MUTEKH, DNA/OS). It also leverages on several existing technologies: on the GAUT [16] and UGH [12] tools for HLS, on the ROMA [35] project for ASIP, on the SYNTOL [26] and BEE [11] tools for source-level analysis and transformations and on the XILINX and ALTERA IP core libraries. Finally it will use the XILINX and ALTERA logic and physical synthesis tools to generate the FPGA configuration bitstreams.

The COACH proposal has been prepared during one year by a technical working group involving the 5 academic partners (one monthly meeting from january 2009 to february 2010). The objective was to analyse the issues of integrating and enhancing the existing tools and tecnnologies into a unique framework. Most of the general software architecture of the proposed design flow (including the exchange format specification) has been define by this working group. Because the COACH project leanes on the ANR SoCLib platform, it may be described as an extension of the SoCLib platform.

Two major FPGA companies are involved in the project: XILINX will contribute as a contractual partner providing documentation and manpower; ALTERA will contribute as a supporter (see letter page 55) providing documentation and development boards. These two companies are strongly motivated to help the COACH project to generate efficient bitsreams for both FPGA families. The role of the industrial partners BULL, THALES, NAVTEL-SYSTEM and FLEXRAS is to provide real use cases to benchmark the COACH design environment and to analyze the designer productivity improvements.

Following the general policy of the SoCLib platform, the COACH project will be an open infrastructure, available in the framework of the SoCLib server. The architectural templates, and the COACH software tools will be distributed under the GPL license. The VHDL synthesizable models for the neutral architectural template (SoCLib IP core library) will be freely available for non commercial use. For industrial exploitation the technology providers are ready to propose commercial licenses, directly to the end user, or through a third party.

Finally, the COACH project is already supported by a large number of PMEs, as demonstrated by the "letters of interest" (see Annex B), that have collected during the preparation of the project : ADACSYS, MDS, INPIXAL, CAMKA System, ATEME, ALSIM, SILICOMP-AQL, ABOUND Logic, EADS-ASTRIUM.

# 2 Context and relevance to the call

Embedded systems (SoC and MPSoC) became an inevitable evolution in the microelectronic industry. Due to the exploding fabrication costs, the ASIC technology (Application Specific Integrated Circuit) is not an option for SMEs (Small and Medium Enterprises). Fortunately, the new FPGA (Field Programmable Gate Array) components, such as the Virtex5 family from XILINX, or the Stratix4 family from ALTERA can implement a complete multi-processor architecture on a single device. But the design of embedded system is a long and complex task that requires expertise in software,

software/hardware partionning, operating system, hardware design, VHDL/Verilog modeling. Only very few SMEs have these multiple expertises and are present on the embedded system market.

The major objective of COACH is to provide to SMEs an open-source framework to design embedded systems on FPGA devices by system designers.

The COACH project will leverage on the expertise gained in the field of virtual prototyping with the SoCLib platform, to propose a new design flow based on a small number of architectural templates. An architectural template is a generic, parameterized architecture, relying on a predefined library of IP cores. Besides using a specific collection of general purpose IP cores (such as processors cores, embedded memory controllers, system bus controllers, I/O and peripheral controllers), each architectural template can be enriched by dedicated hardware coprocessors, obtained by high level synthesis (HLS) tools. During this project, the COACH partners will develop three different architectural templates:

- 1. An ALTERA architectural template based on the ALTERA IP core library, the AVALON system bus and the NIOS processor.

- 2. A XILINX architectural template based on the XILINX IP core library, the PLB system bus and the Microblaze processor.

- 3. A Neutral architectural template based on the SoCLib IP core library and the VCI/OCP communication infrastructure.

The proposed design flow starts from a high level description of the application, specified as a set of parallel tasks written in C, without any assumption on the hardware or software implementation of these tasks. It lets the system designer in charge of expressing the coarse grain parallelism of the application, gives the designer the possibility to explore various mapping of the application on the selected template architecture, and offers a high predictability of results with respect to cost and performance objectives.

When this interactive, system level, design space exploration is completed (converging to a specific mapping on a specific version of the selected architectural template), the rest of the flow is fully automated: The synthesisable VHDL models for the various hardware components, as well as the binary code for the software running on the embedded processors, and the bit-stream to program the the target FPGA will be automatically generated by the COACH tools.

The strength of the COACH approach is the strong integration of the high-level synthesis tools in a platform based design flow supporting virtual prototyping and design space exploration. Most building blocks already exist (resulting from previous projects): the GAUT or UGH synthesis tools, the MUTEKH or DNA embedded operating systems, the ASIP technology, the DSX exploration tool, the MWMR hardware/software communication middleware, the BEE parallelisation tool, as well as the SoCLib library of systemC simulation models. They must now be enhanced and integrated in a consistent design flow.

In HPC (High Performance Computing), the targeted application is an existing application running on a PC. The COACH framework helps designer to accelerate it by migrating critical parts into a SoC embedded into an FPGA device plugged to the PC PCI/X bus.

### The second objective of COACH is to extend the framework to HPC.

This will allow SMEs to enter HPC market for the applications that are unadapted to the current GPU based solutions.

In summary, the COACH project is clearly oriented toward industry, even if most technology building blocks have been previously developed by academic laboratories.

| Segment             | 2010  | 2011  | 2012  |

|---------------------|-------|-------|-------|

| Communications      | 1,867 | 1,946 | 2,096 |

| High end            | 467   | 511   | 550   |

| Consumer            | 550   | 592   | 672   |

| High end            | 53    | 62    | 75    |

| Automotive          | 243   | 286   | 358   |

| High end            | -     | -     | -     |

| Industrial          | 1,102 | 1,228 | 1,406 |

| High end            | 177   | 188   | 207   |

| Military/Aereo      | 566   | 636   | 717   |

| High end            | 56    | 65    | 82    |

| Total FPGA/PLD      | 4,659 | 5,015 | 5,583 |

| Total High-End FPGA | 753   | 826   | 914   |

Table 1: Gartner estimation of worldwide FPGA/PLD consumption (Millions \$)

### 2.1 Economic and societal issues

Microelectronic components allow the integration of complex functions into products, increases commercial attractivity of these products and improves their competitivity. Multimedia and tele-communication sectors have taken advantage from microelectronics facilities thanks to the development of design methodologies and tools for embedded systems. Unfortunately, the Non Recurring Engineering (NRE) costs involded in the design and manufacturing ASICs is very high. An IC foundry costs several billions of euros and the fabrication of a specific circuit costs several millions. For example a conservative estimate for a 65nm ASIC project is 10 million USD. Consequently, it is more and more unaffordable to design and fabricate ASICs for low and medium volume markets.

Today, FPGAs become important actors in the computational domain that was originally dominated by microprocessors and ASICs. Just like microprocessors, FPGA based systems can be reprogrammed on a per-application basis. For many applications, FPGAs offer significant performance benefits over microprocessors implementation. There is still a performance degradation of one order of magnitude versus an equivalent ASIC implementations, but low cost (500 euros to 10K euros), fast time-to-market and flexibility of FPGAs make them an attractive choice for low-to-medium volume applications. Since their introduction in the mid eighties, FPGAs evolved from a simple, low-capacity gate array to devices (ALTERA STRATIX III, XILINX Virtex V) that provide a mix of coarse-grained data path units, memory blocks, microprocessor cores, on chip A/D conversion, and gate counts by millions. This high logic capacity allows to implement complex systems like multi-processors platform with application dedicated coprocessors. Table 1 shows the estimation of the FPGA worldwide market in the next years in various application domains. The "high end" lines concern only FPGA with high logic capacity for complex system implementations. This market is in significant expansion and is estimated to 914 M\$ in 2012.

Today, several companies (Atipa, blue-arc, Bull, Chelsio, Convey, CRAY, DataDirect, DELL, hp, Wild Systems, IBM, Intel, Microsoft, Myricom, NEC, nvidia etc) are making systems where demand for very high performance (HPC) primes over other requirements. They tend to use the highest performing devices like Multi-core CPUs, GPUs, large FPGAs, custom ICs and the most innovative architectures and algorithms. These companies show up in different "traditional" applications and market segments like computing clusters (ad-hoc), servers and storage, networking and Telecom, ASIC emulation and prototyping, military/aereo etc. The HPC market size is estimated today by FPGA providers at 214 M\$. This market is dominated by Multi-core CPUs and GPUs based solutions and the expansion of FPGA-based solutions is limited by the lack of design automation.

Nowadays, there are no commercial or academic tools covering the whole design flow from the system

level specification to the bitstream generation neither for embedded system design nor for HPC.

The aim of the COACH project is to integrate all these design steps into a single design framework and to allow **pure software** developpers to design embedded systems.

The COACH project proposes an open-source framework for mapping multi-tasks software applications on Field Programmable Gate Array circuits (FPGA). It aims to propose solutions to the societal/economical challenges by providing SMEs novel design capabilities enabling them to increase their design productivity with design exploration and synthesis methods that are placed on top of the state-of-the-art methods. We believe that the combination of a design environment dedicated to software developpers and FPGA targets, will allow small and even very small companies to propose embedded system and accelerating solutions for standard software applications with attractive and competitive prices. This new market may explode in the same way as the micro-computer market in the eighties, whose success was due to the low cost of the first micro-processors (compared to main frames) and the advent of high level programming languages which allowed a high number of programmers to launch start-ups in software engineering.

# 2.2 Relevance of the proposal

COACH will contribute to build an open design and run-time environment, including communication middleware and tools to support developers in the production of embedded software, through all phases of the software lifecycle, from requirements analysis downto deployment and maintenance. More specifically, COACH focuses on:

- High level methods and concepts (esp. requirements and architectural level) for system design, development and integration, addressing complexity aspects and modularity.

- Open and modular design environments, enabling flexibility and extensibility by means of new or sector-specific tools and ensuring consistency and traceability along the development lifecycle.

- Light/agile methodologies and adaptive workflow providing a dynamic and adaptive environment, suitable for co-operative and distributed development.

COACH outcome will contribute to strengthen Europe's competitive position by developing technologies and methodologies for product design, focusing (in compliance with the scope of the above program) on technologies, engineering methodologies, novel tools which facilitate resource use efficiency. The COACH approaches and tools will enable new and emerging information technologies for the development, manufacturing and integration of devices and related software into end-products.

The COACH project will benefit from a number of previous recent projects:

- **SOCLIB** The SoCLib ANR platform (2007-2009) is an open infrastructure developped by 10 academic laboratories (TIMA, LIP6, Lab-STICC, IRISA, ENST, CEA-LIST, CEA-LETI, CITI, INRIA-Futurs, LIS) and 6 industrial companies (Thales Communications, Thomson R&D, STMicroelectronics, Silicomp, MDS, TurboConcept). It supports system level virtual prototyping of shared memory, multi-processors architectures, and provides tools to map multi-tasks software application on these architectures, for reliable performance evaluation. The core of this platform is a library of SystemC simulation models for general purpose IP cores such as processors, buses, networks, memories, IO controller. The platform provides also embedded operating systems and software/hardware communication middleware. The synthesisable VHDL models of IPs are not part of the SoCLib platform, and COACH will enhance SoCLib by providing the synthesisable VHDL models required for FPGA synthesis.

- **ROMA** The ROMA ANR project [35] involving IRISA (CAIRN team), LIRMM, CEA List, THOM-SON France R&D, proposes to develop a reconfigurable processor, exhibiting high silicon density

and power efficiency, able to adapt its computing structure to computation patterns that can be speed-up and/or power efficient. The project will borrow from the ROMA ANR project and the ongoing joint INRIA-STMicro Nano2012 project to adapt existing pattern extraction algorithms and datapath merging techniques to ASIP synthesis.

- **TSAR** The TSAR MEDEA+ project (2008-2010) involving BULL, THALES and LIP6 targets the design of a scalable, coherent shared memory, multi-cores processor architecture, and uses the SoCLib plaform for virtual prototyping. COACH will benefit from the synthesizable VHDL models developped in the framework of TSAR (MIPS32 processor core, and RING interconnect).

- **BioWic** On the HPC application side, we also hope to benefit from the experience in hardware acceleration of bioinformatic algorithms/workfows gathered by the CAIRN group in the context of the ANR BioWic project (2009-2011), so as to be able to validate the framework on real-life HPC applications.

The laboratories involved in the COACH project have a well established expertise in the domains:

- In the field of High Level Synthesis (HLS), the project leverages on know-how acquired over the last 15 years with the GAUT [16] project developped by the LAB-STICC laboratory, and with the UGH [12] project developped by the LIP6 and TIMA laboratories.

- Regarding system level architecture, the project is based on the know-how acquired by LIP6 and TIMA in the framework of various projects in the field of communication architectures for shared memory multi-processors systems (COSY [30], DISYDENT [29] or DSPIN [36] of MEDEA-MESA). As an example, the DSPIN project is now used in the TSAR project.

- Regarding Application Specific Instruction Processor (ASIP) design, the CAIRN group at IN-RIA Rennes – Bretagne Atlantique benefits from several years of expertise in the domain of retargetable compiler (Armor/Calife [14] since 1996, and the Gecos compilers [33] since 2002).

- In the field of compilers, the ENS Lyon/LIP Compsys group was founded in 2002 by several senior researchers with experience in high performance computing and automatic parallelization. They have been among the initiators of the polyhedral model, a theory which serve to unify many parallelism detection and exploitation techniques for regular programs. It is expected that the techniques developped by ENS Lyon/LIP for parallelism detection, scheduling [22, 23], process construction [25] and memory management [11] will be very useful as a front-end for HLS tools.

The COACH project answers to several of the challenges found in different axis of the call for proposals.

Axis 1 Architectures des systèmes embarqués

COACH will address new embedded systems architectures by allowing the design of Multi-Core Systems-on-Chip (possibly heterogeneous) on FPGA according to the design constraints and objectives (real-time, low-power). It will permit designing complex SoC based on IP cores (memory, peripherals...), running Embedded Software, as well as an Operating System with associated middleware and API and using hardware accelerator automatically generated. It will also permit to use efficiently different dynamic system management techniques and reconfiguration mechanisms. Thereby COACH well corresponds to axis 1.

### Axis 2 Infrastructures pour l'Internet, le calcul intensif ou les services

COACH will address High-Performance Computing (HPC) by helping designers to accelerate an application running on a PC. By providing tools that translate high level language programs to FPGA configurations, COACH will allow to easily migrate critical parts into an FPGA plugged to the PC bus (through a communication link like PCI/X). Moreover, Dynamic Partial Reconfiguration will be used for improving HPC performance as well as reducing the required area. **Thereby COACH partially corresponds to axis 2**.

### Axis 3 Robotique et contrôle/commande:

COACH will address robotic and control applications by allowing to design complex systems based on MPSoC architecture. Like in the consumer electronics domain, future control applications will employ more and more SoC for safety and security applications. Application domains for such systems are for example automotive or avionics domains (e.g. collision-detection, intelligent navigation...). Manufacturing technology will also increasingly need high-end vision analysis and high-speed robot control. Thereby COACH indirectly answers to axis 3.

### Axis 5 Sécurité et sureté:

The results of the COACH project will help users to build cryptographic secure systems implemented in hardware or both in software/hardware in an effective way, substantially enhancing the process productivity of the cryptographic algorithms hardware synthesis, improving the quality and reducing the design time and the cost of synthesised cryptographic devices. **Thereby COACH indirectly answers to axis 5**.

Finally, it is worth to note that this project covers priorities defined by the commission experts in the field of Information Technolgies Society (IST) for Embedded Systems: <<Concepts, methods and tools for designing systems dealing with systems complexity and allowing to apply efficiently applications and various products on embedded platforms, considering resources constraints (delays, power, memory, etc.), security and quality services>>.

# 3 Scientific and technical Description

### 3.1 State of the Art

Our project covers several critical domains in system design in order to achieve high performance computing. Starting from a high level description we aim at generating automatically both hardware and software components of the system.

### 3.1.1 High Performance Computing

The High-Performance Computing (HPC) world is composed of three main families of architectures: many-core, GPGPU (General Purpose computation on Graphics Unit Processing) and FPGA. The first two families are dominating the market by taking benefit of the strength and influence of mass-market leaders (Intel, Nvidia). In this market, FPGA architectures are emerging and very promising. By adapting architecture to the software, FPGAs architectures enable better performance (typically between x10 and x100 accelerations) while using smaller size and less energy (and heat). However, using FPGAs presents significant challenges [34]. First, the operating frequency of an FPGA is low compared to a high-end microprocessor. Second, based on Amdahl law, HPC/FPGA application performance is unusually sensitive to the implementation quality [19]. Finally, efficient design methodology are required in order to hide FPGA complexity and the underlying implantation subtleties to HPC users, so that they do not have to change their habits and can have equivalent design productivity than in others families [38].

HPC/FPGA hardware is only now emerging and in early commercial stages, but these techniques have not yet caught up. Industrial (Mitrionics [5], Gidel [4], Convey Computer [2]) and academic (CHREC) researches on HPC-FPGA are mainly conducted in the USA. None of the approaches developed in these researches are fulfilling entirely the challenges described above. For example, Convey Computer proposes application-specific instruction set extension of x86 cores in FPGA accelerator, but extension generation is not automated and requires hardware design skills. Mitrionics has an elegant solution based on a compute engine specifically developed for high-performance execution in FPGAs. Unfortunately, the design flow is based on a new programming language (mitrionC) implying important designer efforts and poor portability. Thus, much effort is required to develop design tools that translate high level language programs to FPGA configurations. Moreover, as already remarked in [21], Dynamic Partial Reconfiguration [37] (DPR, which enables changing a part of the FPGA, while the rest is still working) appears very interesting for improving HPC performance as well as reducing required area.

# 3.1.2 System Synthesis

Today, several solutions for system design are proposed and commercialized. The existing commercial or free tools do not cover the whole system synthesis process in a full automatic way. Moreover, they are bound to a particular device family and to IPs library. The most commonly used are provided by ALTERA and XILINX to promote their FPGA devices. These representative tools used to synthesize SoC on FPGA are introduced below.

The XILINX System Generator for DSP [10] is a plug-in to Simulink that enables designers to develop high-performance DSP systems for XILINX FPGAs. Designers can design and simulate a system using MATLAB and Simulink. The tool will then automatically generate synthesizable Hardware Description Language (HDL) code mapped to XILINX pre-optimized algorithms. However, this tool targets only DSP based algorithms, XILINX FPGAs and cannot handle a complete SoC. Thus, it is not really a system synthesis tool.

In the opposite, SOPC Builder [9] from ALTERA and XILINX Platform Studio XPS from XILINX allows to describe a system, to synthesis it, to program it into a target FPGA and to upload a software application. Both SOPC Builder and XPS, allow designers to select and parameterize components from an extensive drop-down list of IP cores (I/O core, DSP, processor, bus core, ...) as well as incorporate their own IP. Nevertheless, all the previously introduced tools do not provide any facilities to synthesize coprocessors and to simulate the platform at a high level (SystemC). System designer must provide the synthesizable description of its own IP-cores with the feasible bus interface. Design Space Exploration is thus limited and SystemC simulation is not possible neither at transactional nor at cycle accurate level.

In addition, XILINX System Generator, XPS and SOPC Builder are closed world since each one imposes their own IPs which are not interchangeable. Designers can then only generate a synthesized netlist, VHDL/Verilog simulation test bench and custom software library that reflect the hardware configuration.

Consequently, a designer developing an embedded system needs to master four different design environments:

- 1. a virtual prototyping environment (in SystemC) for system level exploration,

- 2. an architecture compiler to define the hardware architecture (Verilog/VHDL),

- 3. one or several third-party HLS tools for coprocessor synthesis (C to RTL),

4. and finally back-end synthesis tools for the bit-stream generation (RTL to bitstream).

Furthermore, mixing these tools requires an important interfacing effort and this makes the design process very complex and achievable only by designers skilled in many domains.

### 3.1.3 High Level Synthesis

High Level Synthesis translates a sequential algorithmic description and a set of constraints (area, power, frequency, ...) to a micro-architecture at Register Transfer Level (RTL). Several academic and commercial tools are today available. The most common tools are SPARK [28], GAUT [16], UGH [12] in the academic world and CATAPULTC [1], PICO [7] and CYNTHETIZER [3] in the commercial world. Despite their maturity, their usage is restrained by [18] [13] [17]:

• HLS tools are not integrated into an architecture and system exploration tool. Thus, a designer who needs to accelerate a software part of the system, must adapt it manually to the HLS input dialect and perform engineering work to exploit the synthesis result at the system level,

- Current HLS tools can not target control AND data oriented applications,

- HLS tools take into account mainly a unique constraint while realistic design is multi-constrained. Low power consumption constraint which is mandatory for embedded systems is not yet well handled or not handled at all by the HLS tools already available,

- The parallelism is extracted from initial specification. To get more parallelism or to reduce the amount of required memory in the SoC, the user must re-write the algorithmic specification while there is techniques such as polyedric transformations to increase the intrinsic parallelism,

- While they support limited loop transformations like loop unrolling and loop pipelining, current HLS tools do not provide support for design space exploration neither through automatic loop transformations nor through memory mapping,

- Despite having the same input language (C/C++), they are sensitive to the style in which the algorithm dis written. Consequently, engineering work is required to swap from a tool to another,

- They do not respect accurately the frequency constraint when they target an FPGA device. Their error is about 10 percent. This is annoying when the generated component is integrated in a SoC since it will slow down the whole system.

Regarding these limitations, it is necessary to create a new tool generation reducing the gap between the specification of an heterogeneous system and its hardware implementation [17] [18].

### 3.1.4 Application Specific Instruction Processors

ANR

ASIP (Application-Specific Instruction-Set Processor) are programmable processors in which both the instruction and the micro architecture have been tailored to a given application domain or to a specific application. This specialization usually offers a good compromise between performance (w.r.t a pure software implementation on an embedded CPU) and flexibility (w.r.t an application specific hardware co-processor). In spite of their obvious advantages, using/designing ASIPs remains a difficult task, since it involves designing both a micro-architecture and a compiler for this architecture. Besides, to our knowledge, there is still no available open-source design flow for ASIP design even if such a tool would be valuable in the context of a System Level design exploration tool.

In this context, ASIP design based on Instruction Set Extensions (ISEs) has received a lot of interest [6], as it makes micro architecture synthesis more tractable <sup>1</sup>, and help ASIP designers to focus on compilers, for which there are still many open problems[27]. This approach however has a severe weakness, since it also significantly reduces opportunities for achieving good speedups (most speedups remain between 1.5x and 2.5x), since ISEs performance is generally tied down by I/O constraints as they generally rely on the main CPU register file to access data.

To cope with this issue, recent approaches [32, 31, 15] advocate the use of micro-architectural ISE models in which the coupling between the processor micro-architecture and the ISE component is tightened up so as to allow the ISE to overcome the register I/O limitations. However these approaches generally tackle the problem from a compiler/simulation point of view and do not address the problem of generating synthesizable representations for these models.

We therefore strongly believe that there is a need for an open-framework which would allow researchers and system designers to :

- Explore the various level of interactions between the original CPU micro-architecture and its extension (for example through a Domain Specific Language targeted at micro-architecture specification and synthesis).

- Retarget the compiler instruction-selection pass (or prototype new passes) so as to be able to take advantage of this ISEs.

<sup>&</sup>lt;sup>1</sup>ISEs rely on a template micro-architecture in which only a small fraction of the architecture has to be specialized

- ANR ANR

- Provide a complete System-level Integration for using ASIP as SoC building blocks (integration with application specific blocks, MPSoc, etc.)

## 3.1.5 Automatic Parallelization

The problem of compiling sequential programs for parallel computers has been studied since the advent of the first parallel architectures in the 1970s. The basic approach consists in applying program transformations which exhibit or increase the potential parallelism, while guaranteeing the preservation of the program semantics. Most of these transformations just reorder the operations of the program; some of them modify its data structures. Dependences (exact or conservative) are checked to guarantee the legality of the transformation.

This has lead to the invention of many loop transformations (loop fusion, loop splitting, loop skewing, loop interchange, loop unrolling, ...) which interact in a complicated way. More recently, it has been noticed that all of these are just changes of basis in the iteration domain of the program. This has lead to the introduction of the polyhedral model [24, 20], in which the combination of two transformations is simply a matrix product.

Since hardware is inherently parallel, finding parallelism in sequential programs in an important prerequisite for HLS. The large FPGA chips of today can accomodate much more parallelism than is available in basic blocks. The polyhedral model is the ideal tool for finding more parallelism in loops.

As a side effect, it has been observed that the polyhedral model is a useful tool for many other optimization, like memory reduction and locality improvement. Another point is that the polyhedral domain *stricto sensu* applies only to very regular programs. Its extension to more general programs is an active research subject.

# 3.2 S & T objectives, progress beyond the state of the art

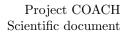

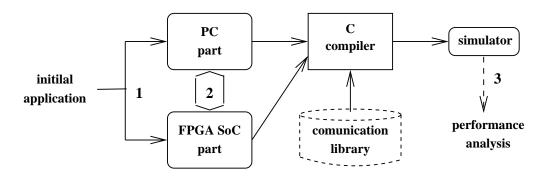

The design steps are presented figure 1.

Figure 1: COACH design flow

**HPC setup:** During this step, the user splits the application into 2 parts: the host application which remains on the PC and the SoC application which is mapped on the FPGA. COACH will provide

a complete simulation model of the whole system (PC+communication+FPGA-SoC) which will allow performance evaluation.

- **SoC design:** In this phase, COACH will allow the user to obtain virtual prototypes for the SoC at different abstraction levels. The user input will consist of a process network describing the coarse grain parallelism of the application, an instance of a generic hardware platform and a mapping of processes on the platform components. COACH will offer different targets to map the processes: software (the process runs as a software task on a SoC processor), ASIP (the process runs as a software task on a SoC processor), and hardware (the process is implemented as a synthesized hardware coprocessor).

- **Application compilation:** Once the SoC architecture is validated through performances analysis, COACH will generate automatically an executable containing the host application and the FPGA bitstream. This bitstream contains both the hardware architecture and the SoC application software. The user will be able to launch the application by loading the bitstream on an FPGA and running the executable on PC.

Hardware/Software co-design is a very complex task. To simplify it, COACH will address the following scientific and technological barriers:

- **Design Space Exploration by Virtual Prototyping**: The COACH environment will allow to easily map a parallel application (formally described as an abstract network of process and communication channels) COACH will permit the system designer to explore the design space, and to define the best hardware/software partitioning of the application.

- Integration of system level modeling and HLS tools : COACH will support the automated generation of hardware accelerators when required by using High-Level Synthesis (HLS) tools. These HLS tools will be fully integrated into a complete system-level design environment. Moreover, COACH will support both data and control dominated applications, and the HLS tools of COACH will support a common language and coding style to avoid re-engineering by the designer. COACH will provide a tool which will automatically explore the micro-architectural design space of coprocessor.

- *High-level code transformation* : COACH will allow to optimize the memory usage, to enhance the parallelism through loop transformations and parallelization. The challenge is to identify the coarse grained parallelism and to generate, from a sequential algorithm, application containing multiple communicating tasks. COACH will adapt techniques which were developed in the 1990 for the construction of distributed programs. However, in the context of HLS, there are several original problems to be solved, related to the FIFO communication channels and with memory optimization. COACH will support code transformation by providing a source to source C2C tool.

- **Unified Hardware/Software communication middleware** : COACH will rely on he SoCLib experience to implement an unified hardware/software communication infrastructure and communication APIs (Application Programming Interface), to support communications between software tasks running on embedded processors and dedicated hardware coprocessors. The main issue here is to support easy migration from a software implementation to an hardware implementation.

- **Processor customization** : ASIP (Application Specific Instruction Processor) design will be addressed by the COACH project. COACH will allow system designers to explore the various level of interactions between the original CPU micro-architecture and its extension. It will also allow to retarget the compiler instruction-selection pass. Finally, COACH will integrate ASIP synthesis in a complete System-level design framework.

The main result is the framework. It is composed concretely of: a communication middleware for HPC, 5 HAS tools (control dominated HLS, data dominated HLS, Coarse grained HLS, Memory optimisation HLS and ASIP), 3 architectural templates that are synthesizable and that can be proto-typed, one design space exploration tool, 2 operating systems (DNA/OS and MUTEKH).

The framework fonctionality will be demonstrated with the demonstrators (see task-7 page 31) and the tutorial example (see task-8 page 4.3.8).

# 4 Scientific and technical objectives / project description

### 4.1 Scientific Programme, Project structure

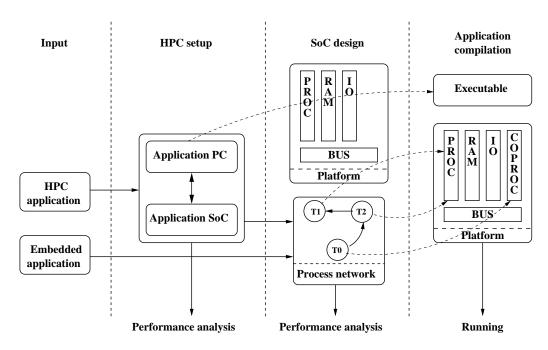

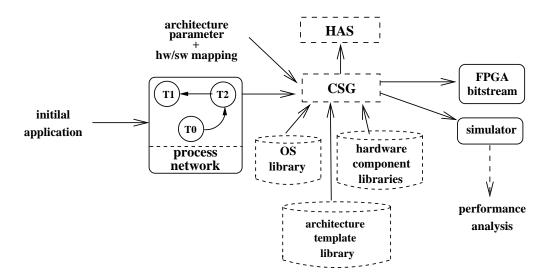

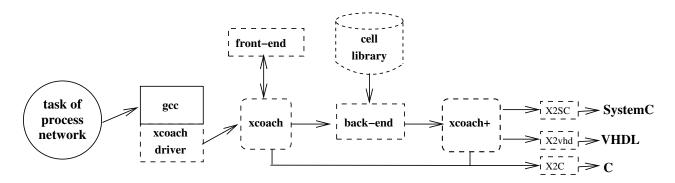

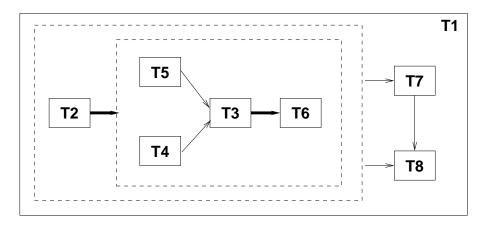

Figures 2, 3 and 4 summarize the software architecture of the COACH framework we will develop. In figures, the dotted boxes are the softwares or formats that COACH has to provide and to support.

For the system generation presented in figure 2, the conductor is the tool CSG (COACH System Generator). Its inputs are a process network describing the target application and the synthesis parameters. The main parameters are the target hardware architectural template with its instantiation parameters, the hardware/software mapping of the tasks, the FPGA device and design constraints. CSG thus requires an architectural template library, an operating system library, two system hardware component (CPU, memories, BUS...) libraries (one for synthesis, one for simulation). For generating the coprocessor of a task mapped as hardware, CSG controls the HAS tools described below. From these inputs CSG can generate the entire system (both software and hardware) either as a SystemC simulator (cycla accurate and/or TLM) to prototype and explore quickly the design space or as a bitstream<sup>2</sup> directly downloadable on the FPGA device<sup>3</sup>.

The software architecture for HAS is presented in figure 3. The input is a single task of the process network. The HAS tools do not work directly on the C++ task description but on an internal format called **xcoach** generated by a plugin into the GNU C compiler (GCC). This will allow on the one hand to insure that all the tools will accept the same C++ description and on the other hand make possible their chaining. The front-end tools read a **xcoach** description and generate a new **xcoach** description that exibits more parallelism or implement specific instructions for ASIP. The back-end tools read an **xcoach** description annotated with hardware information (scheduling, binding) required by the VHDL and systemC drivers. Furthermore, the back-end tools uses a macro-cell library (functional and memory unit).

In addition to digital system design, HPC requires a supplementary partitioning step presented in figure 4. The designer splits the initial application (tag 1) in two parts: one still on the PC and the other running in a FPGA plugged on the PCI/X PC bus. The two parts exchange data through communication primitives (tag 2) implemented in a library. To evaluate the relevance of the partitioning, the designer can build a simulator. Once the partitioning is validated, the design of the FPGA part is done through CSG (figure 2).

The project is split into 8 tasks numbered from 1 to 8. They are described in short below and in detail in section 4.3.

Task-1: Project management This task relates to the monitoring of the COACH project.

- **Task-2:** Backbone infrastructure This task tackles the fundamental points of the project such as the definition of the COACH inputs and outputs, the internal formats (i.e. xcoach and xcoach+) and their associated tools, the architectural templates and the design flow.

- **Task-3:** System generation This task addresses the prototyping and the generation of digital system. Apart from HAS that belongs to task 3 and 4, its components are those presented figure 2 (e.g. CSG, operating systems).

<sup>&</sup>lt;sup>2</sup>COACH generates synthesizable VHDL, and launch the XILINX or ALTERA RTL synthesis tools.

$<sup>^{3}\</sup>mathrm{Additional}$  partial bits treams are generated in case of dynamic partial reconfiguration

Figure 2: Software architecture for digital system generation

Figure 3: Software architecture of hardware accellerator synthesis

Figure 4: Software architecture of HPC

Figure 5: Task dependencies

- **Task-4:** *HAS front-end* This task mainly focusses on four functionalities: optimization of the memory usage, parallelism enhancement through loop transformations, coarse grain parallelization and ASIP generation.

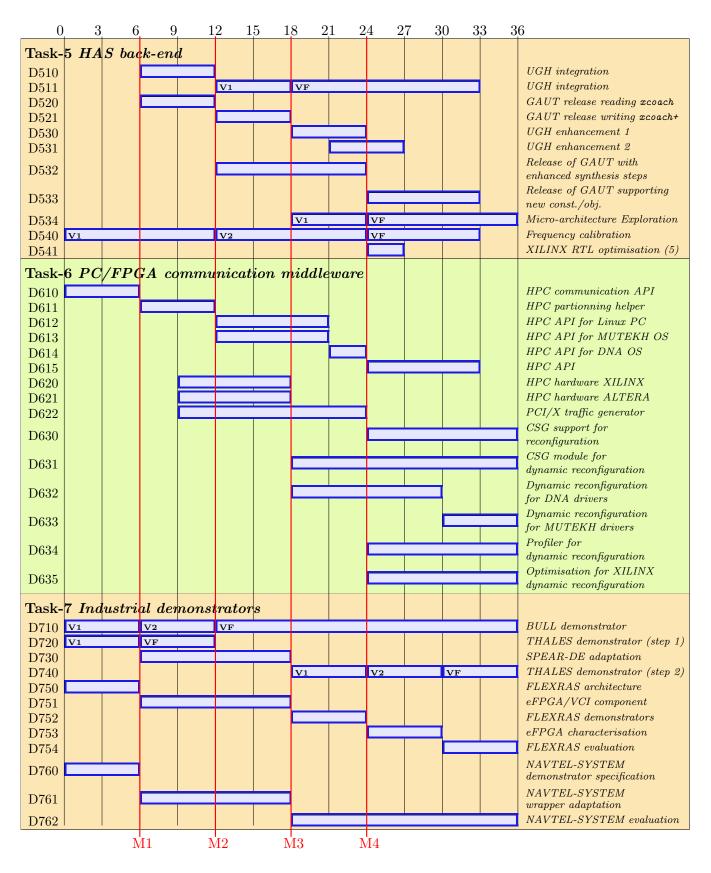

- **Task-5:** *HAS back-end* This task groups two functionalities: High-Level Synthesis of data dominated description and HLS of control dominated description. This task contains also the development of a frequency adaptator that will allow the coprocessors to respect the processor and the bus frequency.

- **Task-6:** *PC/FPGA communication middleware* This task pools the features dedicated to HPC. These are mainly the validation of the partitioning (see figure 4), the system drivers for both PC and FPGA-SoC sides, the hardware communication components and the support for dynamic partial reconfiguration.

- **Task-7:** *Industrial demonstrators* This task groups the demonstrators of the COACH project. Most of them are industrial applications that will be developped within the COACH framework. Others consist in integrating the COACH framework as a driver of industrial proprietary design tools.

- Task 8: *Dissemination* This task concerns the diffusion of the project results. It mainly consists of the production of 4 COACH releases (T0+12, T0+18, T0+24 and T0+36), the publication of a tutorial and user manuals on a WEB site, the publication of research papers in international journals and conferences and the organization of workshops and tutorials in international conferences.

Figure 5 presents the tasks dependencies. " $T_N \longrightarrow T_M$ " means that  $T_N$  impacts the  $T_M$ . The more bold the arrow, the more important is the impact. The graph shows:

- Even though T4 and T5 functionalities are complementary, their developments are independent (thanks to the xcoach internal format).

- T3 slightly depends on T4 and T5. Indeed, T3 may work without T4 and T5 if targeted digital systems do not include hardware accelerators.

- T3 strongly impacts T6 but T3 does not depend at all on T6. Hence demonstrators (T7) of embedded system would not be impacted if T6 would fail.

- T2 drives all the tasks (T3, T4, T5, T6) and is at the heart of the COACH project.

- The demonstrators developped in T7, of course strongly depend on the achievements of the previous tasks (T2, T3, T4, T5, T6).

ANR

• T8 and T1 depend on and impact all the other tasks.

This organisation offers enough robustness to insure the success of the project except for the specification task T2. The only critical task in this chart is T2. However, the partners met 12 times (a one-day meeting per month) during the last year: 10 meetings to exchange and work on scientific and technical aspects and 2 meetings to prepare the project proposal. This gives us a high degree of confidence that T2 will be completed in time.

## 4.2 Project management

- **Project management structure** Each task is assigned to a Task Leader. The Task Leaders assist the project leader in the technical organization, effort management, of the co-operation and the reporting of the progress. A steering committee is composed by task leaders and the project leader. The steering committee has a monthly conference call and is in charge of conflict management if necessary. Each task leader has to report on the main high-lights, major opportunities and problems according to the work-plan. The redaction of the 6-month reports is the responsability of the steering committee. Therefore, each Partner has the responsibility to monthly inform the task Leaders of the current development of the sub-task he has in charge. COACH will be organized in 8 tasks whose interactions are presented in Figure 5.

- Scientific and Technical Reports For every yearly review, a written progress report for each deliverable has to be provided by the task leader to the coordinator for integration in the contractual reports.

- Management of knowledge, Intellectual Property Right (IPR) and Results Exploitation The partners will have to work under eventual NDA constraints. Prior Intellectual Property remains property of the concerned partners. The exploitation of the results obtained in the project and by each partner involved in the consortium will follow the rules written in the articles of the Consortium Agreement accepted and signed by each partner at most 6 months after the project kick-off. To manage the exploitation and dissemination plan within the project, six monthly meetings will analyze the intentions from the consortium (patent, publication...).

- **Management Tools** In order to permit a good management, before the kick-off meeting, each partner will have to identify (name, address, phone, fax and e-mail):

- the financial and administrative contact person,

- the scientific and technical contact person,

- all participants to the project.

A complete and detailed list will be communicated to each partner and to the public Authority. The partners will construct mailing lists for day-to-day communication.

The first task will be the redaction of a Consortium Agreement, dealing mainly with all aspects of the relations between partners, including legal aspects, property rights and further exploitation of the results. This document will be submitted to the partner's financial and legal departments, and will define the management rules (decision level, reporting systems, red flag cases). A first draft of this document will be submitted to each partner during the kick-off meeting.

**Project follow-ups** The basic communication between single project partners will be carried out by means of an Information System (web site), which will be developed and introduced at the very beginning of the project implementation. All scientific and administrative data related to the project will be collected and treated within a specific e-management plate-form accessible directly by the project web site by an individual login and pass-word. The web site will have a few levels of accessibility starting with completely free access, open to broad public up to internal materials available only for members of the consortium for the e-management area.

This communication tools will permit to perform all the reports and to follow as well as possible all the tasks.

**Project monitoring** For this project format and size, a 12 months review by ANR, based on a yearly progress report incorporating milestones reports and deliverables, seems optimum. The internal consortium meetings will be every six months, including a kick-off meeting at the start of the project, in our eyes the most important of all, as it phases the partners for the start of the project.

# 4.3 Description of the tasks

In this document, we use the following abbreviations in the tables and Gantt diagrams:

**partner** INRI for INRIA/CAIRN, LIP for ENS Lyon/LIP, TIMA for TIMA, UBS for LAB-STICC, LIP6 for LIP6, XILX for XILINX, BULL for BULL, TRT for THALES, FLEX for FLEXRAS and NAV for NAVTEL-SYSTEM.

kind of the deliverable x for a software, d for a document and h for a hardware component.

task contribution "lead." for leader and "part." for participant.

other abbreviations "resp." for responsible patrner, "kd" for kind of deliverable.

### 4.3.1 Task 1: Project management

| INRI  | LIP   | TIMA  | UBS   | LIP6  | XILX  | BULL  | TRT   | NAV   | FLEX  |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| part. | part. | part. | part. | lead. | part. | part. | part. | part. | part. |

**Objectives** This task relates to the monitoring of the COACH project. Its main objectives are:

- To ensure the appropriate progress of the project,

- To coordinate the scientific and technical cooperation between the partners,

- To manage and monitor the scientific and technical work and progress in the tasks,

- To verify the conformance to agreed budget and time scales,

- To prepare periodic progress reports in order to control the overall progress of the project,

- To organize the project meetings,

- To set up a shared development infrastructure as a version control system and development WEB site.

${\bf ST1-1}\,$  This sub-task consists in writing and ratifying the consortium agreement.

| number  | date | type | resp. | description                                                                    |

|---------|------|------|-------|--------------------------------------------------------------------------------|

| D110-VF | T0+6 | D    | LIP6  | A document describing the consortium agreement, signed by<br>all the partners. |

ST1-2 This sub-task concerns the global management of the deliverables and of the global organization of the project at all the levels.

| number  | date  | type | resp. | description                                                  |

|---------|-------|------|-------|--------------------------------------------------------------|

| D120-VF | T0+36 | D    | LIP6  | Global management of the project at all the levels: progress |

|         |       |      |       | monitoring, record keeping, meeting organization, review or- |

|         |       |      |       | ganization, the writing of the review reports.               |

**ST1-3** This sub-task consists in managing the project at the partner level. It includes mainly the progress monitoring, the record keeping the participation to the project meetings and the communication with the project leader and the other partners.

| number  | date  | type | resp. | description                              |

|---------|-------|------|-------|------------------------------------------|

| D130-VF | T0+36 |      | LIP6  | Project management at the partner level. |

**ST1-4** This sub-task consists firstly in the building, and next in the administration and the maintenance of the development and dissemination infrastructure. It is also in charge of the COACH releases distribution.

| number  | date    | type | resp. | description                                                   |

|---------|---------|------|-------|---------------------------------------------------------------|

| D140-V1 | T0+6    | X    | LIP6  | Setup of the development infrastructure (version control sys- |

|         |         |      |       | tem configuration, wiki).                                     |

| D140-VF | T0 + 36 | Х    | LIP6  | Standard management of a development infrastructure           |

|         |         |      |       | (adding & suppressing account, retrieving forgotten pass-     |

|         |         |      |       | words, creation and closing development branch, $\dots$ )     |

### 4.3.2 Task 2: Backbone infrastructure

| INRI  | LIP   | TIMA  | UBS   | LIP6  | XILX  | BULL  | TRT   | NAV   | FLEX  |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| part. | part. | part. | part. | lead. | part. | part. | part. | part. | part. |

- **Objectives** This task deals with the main features of digital systems. Its objectives are the specification of the designer input, the definition of the hardware architectural templates and of all the features that the HAS tools will share.

- **ST2-1** This sub-task specifies the COACH environment for the system designer. At this level the COACH framework is a black box. The deliverables are documents specifying: how to feed COACH (the inputs), how to use COACH (the design flow), what is generated (the outputs).

| number  | date    | type | resp. | description                                                   |

|---------|---------|------|-------|---------------------------------------------------------------|

| D210-V1 | T0+6    | D    | LIP6  | The first version of the COACH specification. This doc-       |

|         |         |      |       | ument contains the general description of the framework,      |

|         |         |      |       | the design flow and the description of the architectural tem- |

|         |         |      |       | plates. It refers to the HAS specification (deliverable D212- |

|         |         |      |       | VF) and to the CSG specification (deliverable D211-VF) for    |

|         |         |      |       | the COACH input descriptions.                                 |

| D210-VF | T0+12   | D    | LIP6  | The final version of the D210-V1 deliverable updated with     |

|         |         |      |       | the first feed-backs of the demonstrator sub-tasks.           |

| D211-V1 | T0+6    | D    | TIMA  | The first version of the CSG (COACH System Generator)         |

|         |         |      |       | specification. It specifies how the task graph is described,  |

|         |         |      |       | the communication schemes and its associated API (Appli-      |

|         |         |      |       | cation Programming Interface). The base is the SRL library    |

|         |         |      |       | and the MWMR communication component defined by the           |

|         |         |      |       | SocLib ANR project. Nevertheless, these basic schemes will    |

|         |         |      |       | be enhanced to allow more efficient synthesis.                |

| D211-VF | T0 + 12 | D    | TIMA  | The final version of the D210-V1 deliverable updated with     |

|         |         |      |       | the first feed-backs of the demonstrator sub-tasks.           |

| D212-V1 | T0+6  | D | UBS | The first version of the HAS (Hardware Accelerator Synthesis) specification. It specifies how tasks must be written $(C/C++$ subset) and how communication schemes defined in the D211-VF deliverable must be described for coprocessor synthesis. |

|---------|-------|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D212-VF | T0+12 | D | UBS | The final version of the D210-V1 deliverable updated with the first feed-backs of the demonstrator sub-tasks.                                                                                                                                      |

**ST2-2** This sub-task specifies the software COACH structure. The deliverable is a document listing all the COACH software components and how they cooperate.

| number  | date | type | resp. | description                                                  |

|---------|------|------|-------|--------------------------------------------------------------|

| D220-VF | T0+6 | D    | LIP6  | Description of the software list and the data flow among the |

|         |      |      |       | tools.                                                       |

| <b>ST2-3</b> | This | sub-task | specifies | the | xcoach | and | the | xcoach+ | formats. |

|--------------|------|----------|-----------|-----|--------|-----|-----|---------|----------|

|              |      |          | - r       |     |        |     |     |         |          |

| number  | date    | type | resp. | description                                                   |

|---------|---------|------|-------|---------------------------------------------------------------|

| D230-V1 | T0+6    | D+X  | LIP   | First release of the XML specification of the xcoach format   |

|         |         |      |       | (DTD) and its associated documentation allowing to start      |

|         |         |      |       | HLS tools development.                                        |

| D230-V2 | T0 + 12 | D+X  | LIP   | Second release of XML specification of the xcoach format      |

|         |         |      |       | taking into account the corrections and modifications that    |

|         |         |      |       | the developers of HAS tools suggested.                        |

| D230-VF | T0+18   | D+X  | LIP   | Last release of XML specification of the xcoach format en-    |

|         |         |      |       | hanced with the expression of loop potential parallelism.     |

| D231-V1 | T0+12   | Х    | UBS   | A GCC plugin C2X that generates a xcoach description (de-     |

|         |         |      |       | fined in D230-V1 deliverable) from a C/C++ task descrip-      |

|         |         |      |       | tion (defined in D212-VF deliverable).                        |

| D231-VF | T0+18   | Х    | UBS   | An updated version of C2X (D231-V1) which supports the        |

|         |         |      |       | xcoach format defined in the D230-VF deliverable and the      |

|         |         |      |       | HAS input format defined in the D212-VF deliverable.          |

| D232-V1 | T0 + 12 | Х    | UBS   | This second tool X2C regenerates a C description from a       |

|         |         |      |       | xcoach description.                                           |

| D232-VF | T0 + 18 | Х    | UBS   | The same software as the former (D232-V1) but for the         |

|         |         |      |       | xcoach format as defined in the D230-VF deliverable and       |

|         |         |      |       | HAS input as defined in the D212-VF deliverable.              |

| D233-V1 | T0+18   | Х    | LIP6  | The first release of the software tool X2SC that translates   |

|         |         |      |       | xcoach+ description to CABA and TLM-DT SystemC mod-           |

|         |         |      |       | ule.                                                          |

| D233-VF | T0+24   | Х    | LIP6  | Final release of the former software (D233-V1).               |

| D234-V1 | T0+18   | Х    | UBS   | The first release of the software tool X2VHDL that translates |

|         |         |      |       | <b>xcoach+</b> description to synthesizable VHDL description. |

| D234-VF | T0 + 24 | Х    | UBS   | Final release of the former software (D234-V1) and integra-   |

|         |         |      |       | tion of enhancements proposed in D235 deliverable.            |

| D235-VF | T0+21 | D | XILX | This deliverable consists in optimizing the VHDL generated |

|---------|-------|---|------|------------------------------------------------------------|

|         |       |   |      | from xcoach+ format (deliverable D234) for the XILINX      |

|         |       |   |      | RTL synthesis tools. LAB-STICC will provide several ex-    |

|         |       |   |      | amples of VHDL source files generated from xcoach+, with   |

|         |       |   |      | explanations about generation process of main data struc-  |

|         |       |   |      | tures used in VHDL sources, XILINX will provide back a     |

|         |       |   |      | documentation listing that proposes VHDL generation en-    |

|         |       |   |      | hancements.                                                |

ST2-4 This sub-task aims to define a tool in order to pilot the GCC/xcoach compiler.

| number  | date  | type | resp. | description                           |

|---------|-------|------|-------|---------------------------------------|

| D240-VF | T0+3  | D    | UBS   | Specification of the GCC driver tool. |

| D241-V1 | T0+9  | Х    | UBS   | First release of the GCC driver tool. |

| D241-VF | T0+12 | Х    | UBS   | Final release of the GCC driver tool. |

**ST2-5** Backend HLS tools use a characterized macro-cell library to build the micro-architecture of a coprocessor. The characterisation of a cell depends on the target device. The role of this sub-task is to define the macro-cells and to provite a tool that characterizes them automatically by synthesizing them and by extracting their delays. This is done by using RTL synthesis.

| number  | date  | type | resp. | description                                                   |

|---------|-------|------|-------|---------------------------------------------------------------|

| D250-VF | T0+6  | D    | UBS   | Definition of the macro cells and the file format describing  |

|         |       |      |       | them.                                                         |

| D251-VF | T0+12 | Х    | UBS   | Final release of the software tool that generates automati-   |

|         |       |      |       | cally the characterized macro-cell library for a FPGA device. |

### 4.3.3 Task 3: System generation

| INRI  | LIP | TIMA  | UBS   | LIP6  | XILX  | BULL | TRT | NAV | FLEX |

|-------|-----|-------|-------|-------|-------|------|-----|-----|------|

| part. |     | part. | part. | lead. | part. |      |     |     |      |

- **Objectives** This task deals with the prototyping and the generation of FPGA-SoC digital systems. Its is described on figure 2. Its objective is to allow the system designer to explore the design space by quickly prototyping and then to automatically generate the FPGA-SoC systems. This task consists of

- The development of all the missing components (SytemC models and/or synthesizable VHDL models of the IP-cores),

- The configuration and the development of drivers of the operating systems (Board Support Package, HAL),

- The CSG software that generates the SystemC simulators for prototyping and the FPGA-SoC system including its bitstream and software executable code,

- The specification of enhanced communication schemes and their sofware and hardware implementations.

This task being based on the SoCLib platform, a first release will be delivered at T0 + 12 to allow the demonstrators to start working. This release will include the standard communication schemes (based on SoCLib MWMR component) and support the neutral architectural template for prototyping and hardware generation.

| number  | date    | type | resp. | description                                                |

|---------|---------|------|-------|------------------------------------------------------------|

| D310-V1 | T0+12   | Х    | LIP6  | The first software release of the CSG tool that will allow |

|         |         |      |       | demonstrators to start working by using the neutral archi- |