## Les GPIO du PIC16F877

cours n°3 LI326

# GPIO: General Purpose Input/Output

Selon Wikipedia:

- Les ports GPIO (General Purpose Input/Output, c'est-à-dire entrée/sortie pour un usage général) sont des ports d'entrée/sortie très utilisés dans le monde des microcontrôleurs, en particulier dans le domaine de l'électronique embarquée. Les périphériques GPIO comportent un ensemble de ports d'entrée/sortie qui peuvent être configurés pour jouer soit le rôle d'une entrée, soit le rôle d'une sortie.

- Lorsqu'un port GPIO est configuré en tant que sortie, on peut écrire dans un registre interne afin de modifier l'état d'une sortie. Lorsqu'il est configuré en tant qu'entrée, on peut détecter son état en lisant le contenu d'un registre interne.

- De plus, les périphériques GPIO peuvent produire des interruptions et des événements d'accès direct à la mémoire.

### Plan

- Les GPIO du pic

- Lecture de la documentation

- Usages

- $\circ$  Commande de LEDs

- Afficheur 7-segments

- $\circ$  Bouton poussoir

- $\circ$  Clavier matriciel

- $\circ$  Clavier 1 fil

| /                                          | File<br>Address | /                                                      | File<br>Address   |                                                        | File<br>Address |                                            | File<br>Addres       |

|--------------------------------------------|-----------------|--------------------------------------------------------|-------------------|--------------------------------------------------------|-----------------|--------------------------------------------|----------------------|

| Indirect addr.(*)                          | 00h             | Indirect addr.(*)                                      | 80h               | Indirect addr.(*)                                      | 100h            | Indirect addr.(*)                          | 180h                 |

| TMR0                                       | 01h             | OPTION_REG                                             | 81h               | TMR0                                                   | 101h            | OPTION_REG                                 | 181h                 |

| PCL                                        | 02h             | PCL                                                    | 82h               | PCL                                                    | 102h            | PCL                                        | 182h                 |

| STATUS                                     | 03h             | STATUS                                                 | 83h               | STATUS                                                 | 103h            | STATUS                                     | 183h                 |

| FSR                                        | 04h             | FSR                                                    | 84h               | FSR                                                    | 104h            | FSR                                        | 184h                 |

| PORTA                                      | 05h             | TRISA                                                  | 85h               |                                                        | 105h            |                                            | 185h                 |

| PORTB                                      | 06h             | TRISB                                                  | 86h               | PORTB                                                  | 106h            | TRISB                                      | 186h                 |

| PORTC                                      | 07h             | TRISC                                                  | 87h               |                                                        | 107h            |                                            | 187h                 |

| PORTD <sup>(1)</sup>                       | 08h             | TRISD <sup>(1)</sup>                                   | 88h               |                                                        | 108h            |                                            | 188h                 |

| PORTE <sup>(1)</sup>                       | 09h             | TRISE <sup>(1)</sup>                                   | 89h               |                                                        | 109h            |                                            | 189h                 |

| PCLATH                                     | 0Ah             | PCLATH                                                 | 8Ah               | PCLATH                                                 | 10Ah            | PCLATH                                     | 18Ah                 |

| INTCON                                     | 0Bh             | INTCON                                                 | 8Bh               | INTCON                                                 | 10Bh            | INTCON                                     | 18Bh                 |

| PIR1                                       | 0Ch             | PIE1                                                   | 8Ch               | EEDATA                                                 | 10Ch            | EECON1                                     | 18Ch                 |

| PIR2                                       | 0Dh             | PIE2                                                   | 8Dh               | EEADR                                                  | 10Dh            | EECON2                                     | 18Dh                 |

| TMR1L                                      | 0Eh             | PCON                                                   | 8Eh               | EEDATH                                                 | 10Eh            | Reserved <sup>(2)</sup>                    | 18Eh                 |

| TMR1H                                      | 0Fh             |                                                        | 8Fh               | EEADRH                                                 | 10Fh            | Reserved <sup>(2)</sup>                    | 18Fh                 |

| T1CON                                      | 10h             |                                                        | 90h               |                                                        | 110h            |                                            | 190h                 |

| TMR2                                       | 11h             | SSPCON2                                                | 91h               |                                                        | 111h            |                                            | 191h                 |

| T2CON                                      | 12h             | PR2                                                    | 92h               |                                                        | 112h            |                                            | 192h                 |

| SSPBUF                                     | 13h             | SSPADD                                                 | 93h               |                                                        | 113h            |                                            | 193h                 |

| SSPCON                                     | 14h             | SSPSTAT                                                | 94h               |                                                        | 114h            |                                            | 194h                 |

| CCPR1L                                     | 15h             |                                                        | 95h               |                                                        | 115h            |                                            | 195h                 |

| CCPR1H                                     | 16h             |                                                        | 96h               |                                                        | 116h            |                                            | 196h                 |

| CCP1CON                                    | 17h             |                                                        | 97h               | General                                                | 117h            | General                                    | 197h                 |

| RCSTA                                      | 18h             | TXSTA                                                  | 98h               | Purpose                                                | 118h            | Purpose                                    | 198h                 |

| TXREG                                      | 19h             | SPBRG                                                  | 99h               | Register<br>16 Bytes                                   | 119h            | Register<br>16 Bytes                       | 199h                 |

| RCREG                                      | 1Ah             | 0. 5.10                                                | 9Ah               | 10 Dytes                                               | 11Ah            | 10 2 3 10 3                                | 19Ah                 |

| CCPR2L                                     | 1Bh             |                                                        | 9Bh               |                                                        | 11Bh            |                                            | 19Bh                 |

| CCPR2H                                     | 1Ch             |                                                        | 9Ch               |                                                        | 11Ch            |                                            | 19Cł                 |

| CCP2CON                                    | 1Dh             |                                                        | 9Dh               |                                                        | 11Dh            |                                            | 19Dł                 |

| ADRESH                                     | 1Eh             | ADRESL                                                 | 9Eh               |                                                        | 11Eh            |                                            | 19Eh                 |

| ADCON0                                     | 1Fh             | ADCON1                                                 | 9Fh               |                                                        | 11Fh            |                                            | 19Fh                 |

| ADCONU                                     | 20h             | ADCONT                                                 |                   |                                                        | 120h            |                                            |                      |

| General<br>Purpose<br>Register<br>96 Bytes |                 | General<br>Purpose<br>Register<br>80 Bytes<br>accesses | A0h<br>EFh<br>F0h | General<br>Purpose<br>Register<br>80 Bytes<br>accesses | 16Fh<br>170h    | General<br>Purpose<br>Register<br>80 Bytes | 1A0h<br>1EFh<br>1F0h |

|                                            | 7Eb             | 70h-7Fh                                                | EEb               | 70h-7Fh                                                | 17Fh            | 70h - 7Fh                                  | 1656                 |

| Bank 0                                     | 7Fh             | Bank 1                                                 | FFh               | Bank 2                                                 | 1/FN            | Bank 3                                     | 1FF                  |

Registres impliqués

- 5 ports: A,B,C,D,E

- Tous les ports ne sont pas égaux.

- Certains ports peuvent lever des interruptions.

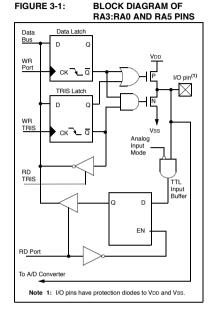

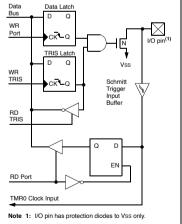

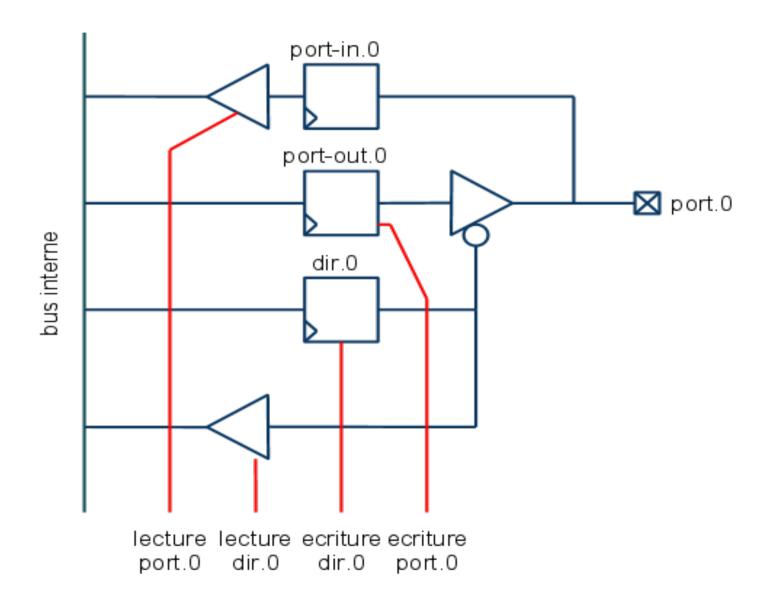

## La documentation officielle

Pour chaque port:

- Une description de la fonction

- Un schéma représentatif du comportement

- La liste des registres impliqués

- La définition des registres spéciaux généraux se trouve aussi dans le chapitre sur la mémoire

#### PIC16F87X

#### 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register(1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ;                       |

|-------|---------|-----|-------------------------|

| BCF   | STATUS, | RP1 | ; Bank0                 |

| CLRF  | PORTA   |     | ; Initialize PORTA by   |

|       |         |     | ; clearing output       |

|       |         |     | ; data latches          |

| BSF   | STATUS, | RP0 | ; Select Bank 1         |

| MOVLW | 0x06    |     | ; Configure all pins    |

| MOVWF | ADCON1  |     | ; as digital inputs     |

| MOVLW | 0xCF    |     | ; Value used to         |

|       |         |     | ; initialize data       |

|       |         |     | ; direction             |

| MOVWF | TRISA   |     | ; Set RA<3:0> as inputs |

|       |         |     | ; RA<5:4> as outputs    |

|       |         |     | ; TRISA<7:6>are always  |

|       |         |     | ; read as '0'.          |

| 1     |         |     |                         |

FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

#### **PIC16F87X**

#### TABLE 3-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------------------------------|-------|-------|-------|---------|---------|--------------------------|---------------------------------|

| 05h     | PORTA  | -     |       | RA5                           | RA4   | RA3   | RA2   | RA1     | RA0     | 0x 0000                  | Ou 0000                         |

| 85h     | TRISA  | -     |       | PORTA Data Direction Register |       |       |       | 11 1111 | 11 1111 |                          |                                 |

| 9Fh     | ADCON1 | ADFM  | 1     | -                             | -     | PCFG3 | PCFG2 | PCFG1   | PCFG0   | 0- 0000                  | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as ' 0' . Shaded cells are not used by PORTA.

| Note: | When using the SSP module in SPI Slave mode and SS enabled, the A/D converter must be set to one of |  |

|-------|-----------------------------------------------------------------------------------------------------|--|

|       | the following modes, where PCFG3:PCFG0 = 0100,0101, 011x, 1101, 1110, 1111.                         |  |

#### GPIO exemple du port D

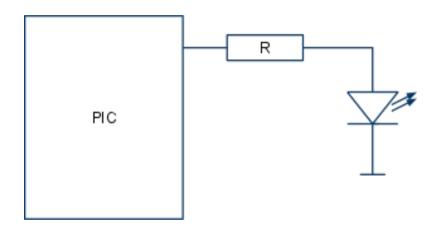

## Affichage par LEDs

- 1 sur la broche allume la LED

- 0 éteint la LED

- La résistance permet de limiter le courant (entre 2 et 20mA)

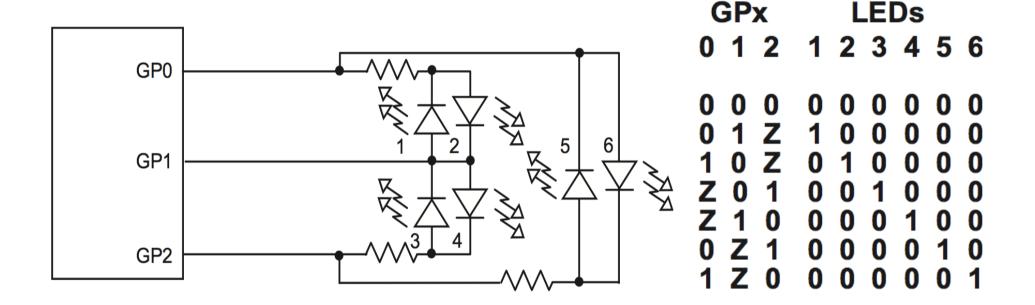

#### Commandes 6 LEDs

Les GPIOs peuvent avoir 3 états : 0, 1 et Z

Ici, on peut allumer 1 led parmi les 6.

En généralisant, avec GP ports, on peut commander GP\*(GP-1) LEDs

• 2 LEDs avec 2 GPs, 6 avec 3, 12 avec 4, 20 avec 5, ...

### Multiplexage temporel

- Les LEDs s'allument et s'éteignent instantanément.

- L'œil humain ne distingue pas les clignotements > à 100Hz.

- Si on allume les LEDs à tour de rôle à une fréquence supérieure à 100Hz on peut "voir" plusieurs leds allumées.

- avec 6 leds:

|                | •          |            | inférieur à | 0,01 secon  | de          |            | -          |            | inférieur à 0,01 seconde |             |             |            |  |  |

|----------------|------------|------------|-------------|-------------|-------------|------------|------------|------------|--------------------------|-------------|-------------|------------|--|--|

|                | L1         | L2         | L3          | L4          | L5          | L6         | L1         | L2         | L3                       | L4          | L5          | L6         |  |  |

|                |            |            |             |             |             |            |            |            |                          |             |             |            |  |  |

|                |            |            |             |             |             |            |            |            | 1                        |             |             |            |  |  |

|                |            |            |             |             |             |            |            |            |                          |             |             |            |  |  |

|                |            |            |             | _           | <u> </u>    |            |            |            |                          |             |             |            |  |  |

|                |            |            |             |             |             | <u> </u>   |            |            |                          |             |             |            |  |  |

|                |            |            |             |             |             |            | <u> </u>   |            |                          |             |             |            |  |  |

| 055            | 000        |            | :           |             |             |            | 1          |            | :                        |             | 000         |            |  |  |

| OFF<br>ON      | 000<br>Z10 | 000<br>Z01 | 000<br>10Z  | 000<br>01 Z | 000<br>1 Z0 | 000<br>0Z1 | 000<br>Z10 | 000<br>Z01 | 000<br>10Z               | 000<br>01 Z | 000<br>1 Z0 | 000<br>0Z1 |  |  |

| P[20]<br>T[20] | 010<br>100 | 001<br>100 | 100<br>001  | 010<br>001  | 100<br>010  | 001<br>010 | 010<br>100 | 001<br>100 | 100<br>001               | 010<br>001  | 100<br>010  | 001<br>010 |  |  |

# Algorithme d'affichage

soit

- Vaff une valeur sur 6 bits à afficher

- Baff le numéro du bit à afficher (sera compris entre 0 et 5)

- Paff un tableau de 6 cases avec les codes à mettre sur les Ports pour afficher 1 Paff [6] = {010,001,100,010,100,001};

- Taff un tableau de 6 cases avec les codes à mettre sur les Dir (Tris) pour afficher 1 Taff [6] = {100,100,001,001,010,010};

- P La valeur du port

- T La direction du port

algo:

```

faire périodiquement (p. ex. 10ms)

P = 0; T = 0;

si ((Vaff >> Baff) & 1) alors

T = Taff [ Baff ];

P = Paff [ Baff ];

finsi

Baff = ( Baff + 1 ) % 6;

finfaire

```

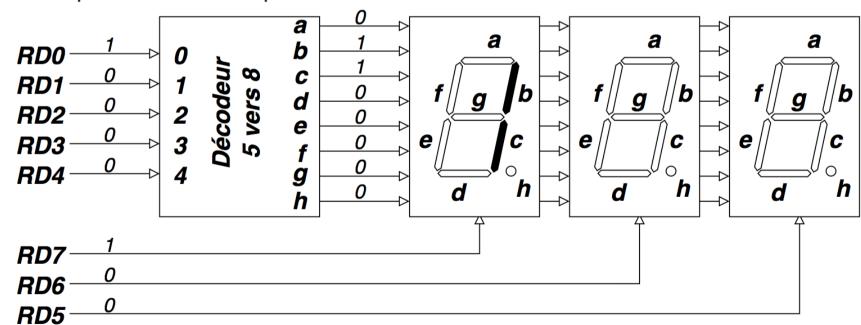

### Afficheurs 7 segments

commande de 3 afficheurs 7-segments (branchés sur le port D) grâce au multiplexage temporel.

Par exemple, si le PORTD présente la valeur B'1000001', cela affiche « 1\_- »

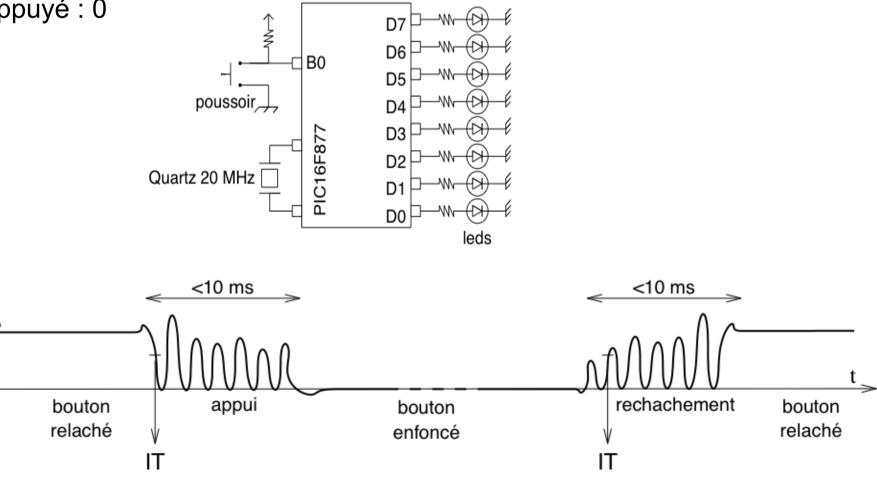

### Le bouton poussoir

Une entrée sur 1 bit numérique:

- relaché : 1

- appuyé : 0

V 5

0

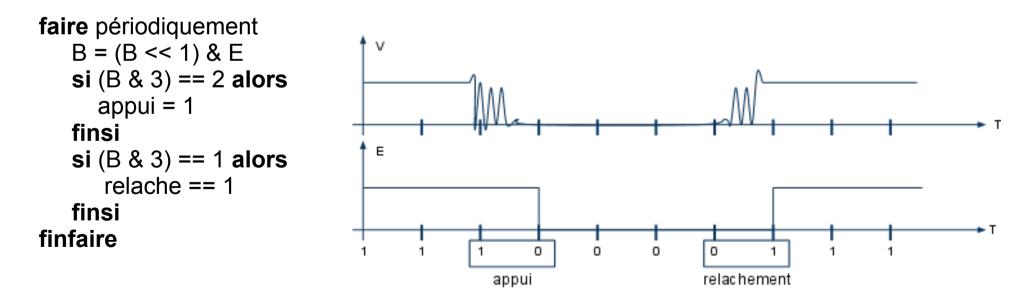

#### Traitement des rebonds

Il suffit d'échantillonner à une période supérieure aux rebonds, mais inférieure à la durée d'appui

#### soit

- B : une variable

- E : la valeur du bouton poussoir

- appui : un drapeau à 1 si appui

- relache : un drapeau à 1 si relachement

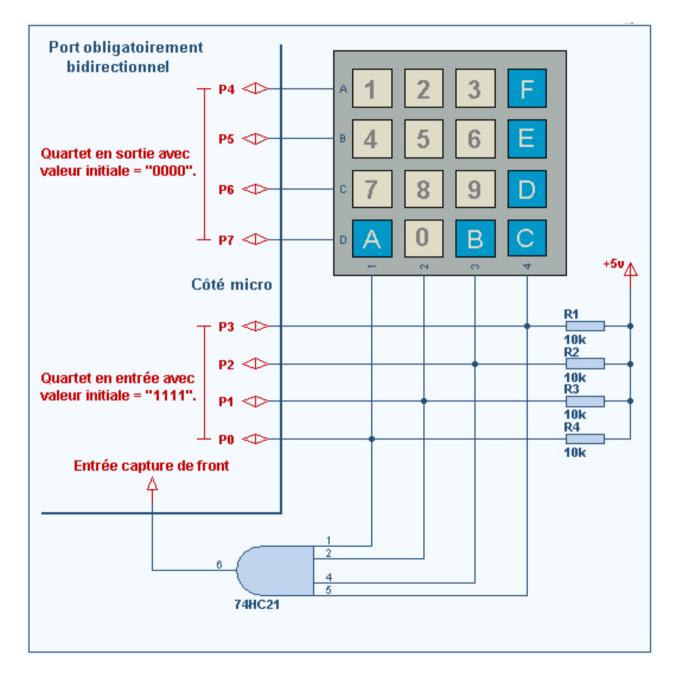

## **Clavier matriciel**

P4 à P7 à 0 permet de détecter un appui

puis on place une des lignes à 0 les autres en entrée et on lit P0 à P3

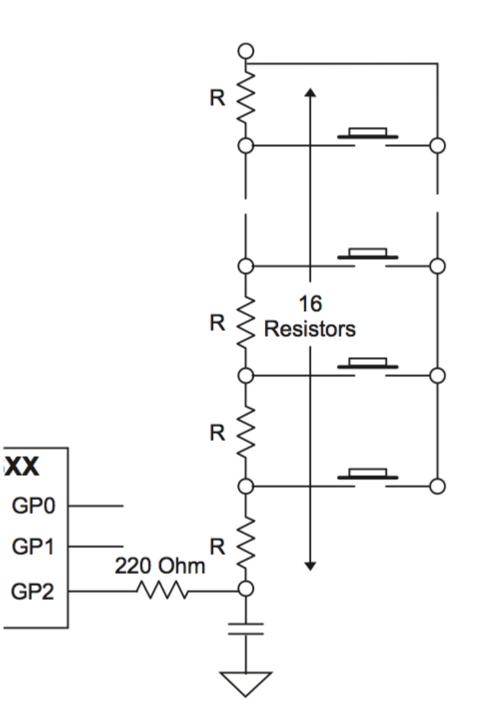

## clavier 1 fil

- La charge d'une capacité est "proportionnelle" à la résistance de charge : si on double la resistance on double le temps de charge

- Algorithme GP2 = 0 compteur = 0 GP2 est mis en entrée tantque GP2 != 1 compteur++ fintantque touche = fct(compteur)

garder les 4 bits de poids forts du compteur