## 12.0 SPECIAL FEATURES OF THE CPU

All PIC16F87X devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87X devices have a Watchdog Timer, which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. The erased, or unprogrammed value of the configuration word is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

## PIC16F87X

### REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| CP1      | CP0    | DEBUG                  | —                                                                                                          | WRT      | CPD       | LVP               | BODEN                         | CP1       | CP0      | PWRTE            | WDTE | F0SC1 | F0S0 |

|----------|--------|------------------------|------------------------------------------------------------------------------------------------------------|----------|-----------|-------------------|-------------------------------|-----------|----------|------------------|------|-------|------|

| bit13    |        |                        |                                                                                                            |          |           |                   |                               |           |          |                  |      |       | b    |

| bit 13-1 | 2      | CP1·CP0                | CP1:CP0: FLASH Program Memory Code Protection bits <sup>(2)</sup>                                          |          |           |                   |                               |           |          |                  |      |       |      |

| bit 5-4  | 2,     | 11 = Cod               |                                                                                                            | 0        | Weme      | y 0000            | 1 1010010111                  | 110       |          |                  |      |       |      |

| DIL 5-4  |        |                        |                                                                                                            |          | protecte  | ed (PIC           | 16F877, 876                   | )         |          |                  |      |       |      |

|          |        | 10 = 0F00              | 10 = 1F00h to 1FFFh code protected (PIC16F877, 876)<br>10 = 0F00h to 0FFFh code protected (PIC16F874, 873) |          |           |                   |                               |           |          |                  |      |       |      |

|          |        | 01 = 1000              | h to 1Fl                                                                                                   | FFh code | protecte  | ed (PIC           | 16F877, 876                   | )         |          |                  |      |       |      |

|          |        |                        | 01 = 1000h to 1FFFh code protected (PIC16F877, 876)<br>01 = 0800h to 0FFFh code protected (PIC16F874, 873) |          |           |                   |                               |           |          |                  |      |       |      |

|          |        |                        |                                                                                                            |          | •         | · ·               | 16F877, 876                   | <i>,</i>  |          |                  |      |       |      |

|          |        | 00 = 0000              |                                                                                                            | -Fn code | protecte  | ed (PIC           | 16F874, 873                   | )         |          |                  |      |       |      |

| bit 11   |        | DEBUG:                 |                                                                                                            |          |           |                   | DD7                           |           |          | <b>D</b> = i = = |      |       |      |

|          |        |                        |                                                                                                            |          |           |                   | RB7 are ge<br>RB7 are de      |           |          |                  |      |       |      |

|          |        |                        |                                                                                                            |          |           | Do anu            |                               | licateu i | o the de | buggei.          |      |       |      |

| bit 10   |        | Unimpler               | nented:                                                                                                    | Read as  | 1         |                   |                               |           |          |                  |      |       |      |

| bit 9    |        | WRT: FLA               |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

|          |        |                        |                                                                                                            |          |           |                   | written to by<br>be written t |           |          |                  |      |       |      |

|          |        | •                      | •                                                                                                          | 0        | ,         |                   | be written t                  |           |          |                  |      |       |      |

| bit 8    |        | CPD: Dat               |                                                                                                            |          | de Prote  | ection            |                               |           |          |                  |      |       |      |

|          |        | 1 = Code<br>0 = Data I |                                                                                                            |          | v codo r  | rotocto           | 4                             |           |          |                  |      |       |      |

|          |        |                        |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

| bit 7    |        |                        |                                                                                                            |          |           |                   | nming Enabl<br>oltage progr   |           | onables  |                  |      |       |      |

|          |        |                        |                                                                                                            |          |           |                   | e used for p                  |           |          | I                |      |       |      |

| 1.11.0   |        |                        | -                                                                                                          |          |           |                   |                               | - 3       |          |                  |      |       |      |

| bit 6    |        | 1 = BOR                |                                                                                                            | ut Reset | Enable    | Ditter            |                               |           |          |                  |      |       |      |

|          |        | 1 = BOR (              |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

|          |        | -                      |                                                                                                            |          |           | (2)               |                               |           |          |                  |      |       |      |

| bit 3    |        | PWRTE:                 |                                                                                                            |          | Enable b  | it <sup>(3)</sup> |                               |           |          |                  |      |       |      |

|          |        | 1 = PWR<br>0 = PWR     |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

| 1.11.0   |        |                        |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

| bit 2    |        | 1 = WDT                |                                                                                                            |          | nable bit |                   |                               |           |          |                  |      |       |      |

|          |        | 0 = WDT                |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

| 1.1.4.6  |        |                        |                                                                                                            |          | <b>.</b>  |                   |                               |           |          |                  |      |       |      |

| bit 1-0  |        | FOSC1:F<br>11 = RC (   |                                                                                                            |          | Selectio  | n Dits            |                               |           |          |                  |      |       |      |

|          |        | 10 = HS c              |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

|          |        | 01 = XT c              |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

|          |        | 00 = LP o              |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

|          |        |                        |                                                                                                            |          |           |                   |                               |           |          |                  |      |       |      |

| Noto '   | 1. Tha | oracod (up             | program                                                                                                    | mod) vol | up of the | confic            | uration word                  |           | 'n       |                  |      |       |      |

| NOLE     |        | of the CP1:C           |                                                                                                            |          |           |                   | aration word                  | 13 35 65  |          |                  |      |       |      |

Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), r Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled

### 12.2 Oscillator Configurations

12.2.1 OSCILLATOR TYPES

The PIC16F87X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

- 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

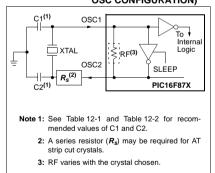

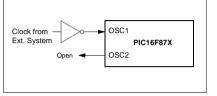

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F87X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 12-2).

#### FIGURE 12-1: CRYSTAL/CERAMIC (HS. XT OR LP

## **RESONATOR OPERATION OSC CONFIGURATION)**

FIGURE 12-2: EXTERNAL CLOCK INPUT **OPERATION (HS. XT OR** LP OSC CONFIGURATION)

### TABLE 12-1: CERAMIC RESONATORS

| Ranges Tested: |                                 |                                         |                          |  |  |  |  |  |

|----------------|---------------------------------|-----------------------------------------|--------------------------|--|--|--|--|--|

| Mode           | Freq.                           | OSC1                                    | OSC2                     |  |  |  |  |  |

| ХТ             | 455 kHz<br>2.0 MHz<br>4.0 MHz   | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |                          |  |  |  |  |  |

| HS             | 8.0 MHz<br>16.0 MHz             | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF |  |  |  |  |  |

|                | ues are for de<br>following Tab | <b>esign guidance</b><br>le 12-2.       | only.                    |  |  |  |  |  |

|                | Resona                          | ators Used:                             |                          |  |  |  |  |  |

| 455 kHz        | Panasonic E                     | ± 0.3%                                  |                          |  |  |  |  |  |

| 2.0 MHz        | Murata Erie CSA2.00MG ± 0.5%    |                                         |                          |  |  |  |  |  |

| 4.0 MHz        | Murata Erie CSA4.00MG ± 0.5%    |                                         |                          |  |  |  |  |  |

| 8.0 MHz        | Murata Erie CSA8.00MT ± 0.5%    |                                         |                          |  |  |  |  |  |

| 16.0 MHz       | Murata Erie                     | CSA16.00MX                              | ± 0.5%                   |  |  |  |  |  |

All resonators used did not have built-in capacitors.

## **PIC16F87X**

### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc Type   | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|------------|------------------|------------------|------------------|

| LP         | 32 kHz           | 33 pF            | 33 pF            |

|            | 200 kHz          | 15 pF            | 15 pF            |

| XT         | 200 kHz          | 47-68 pF         | 47-68 pF         |

|            | 1 MHz            | 15 pF            | 15 pF            |

|            | 4 MHz            | 15 pF            | 15 pF            |

| HS         | 4 MHz            | 15 pF            | 15 pF            |

|            | 8 MHz            | 15-33 pF         | 15-33 pF         |

|            | 20 MHz           | 15-33 pF         | 15-33 pF         |

| These valu | les are for o    | lesion quidance  | e only.          |

See notes following this table.

|         | Crystals Used              |          |

|---------|----------------------------|----------|

| 32 kHz  | Epson C-001R32.768K-A      | ± 20 PPM |

| 200 kHz | STD XTL 200.000KHz         | ± 20 PPM |

| 1 MHz   | ECS ECS-10-13-1            | ± 50 PPM |

| 4 MHz   | ECS ECS-40-20-1            | ± 50 PPM |

| 8 MHz   | EPSON CA-301 8.000M-C      | ± 30 PPM |

| 20 MHz  | EPSON CA-301 20.000M-<br>C | ± 30 PPM |

- Note 1: Higher capacitance increases the stability of oscillator, but also increases the startup time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 3: R<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: When migrating from other PICmicro devices, oscillator performance should be verified.

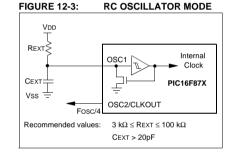

#### 12.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F87X.

## 12.3 RESET

The PIC16F87X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 12-4. These bits are used in software to determine the nature of the RESET. See Table 12-6 for a full description of RESET states of all registers.

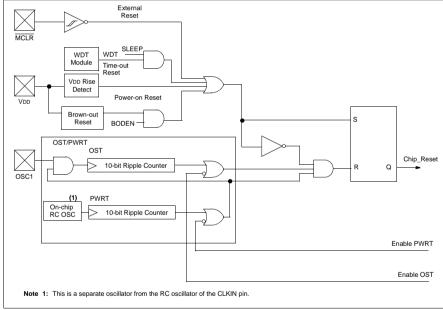

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-4.

These devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

### FIGURE 12-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## PIC16F87X

## 12.4 Power-On Reset (POR)

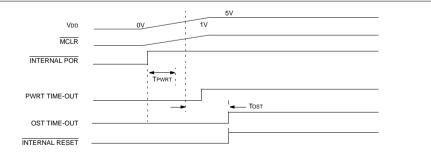

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the  $\overline{MCLR}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to Application Note, AN007, "Power-up Trouble Shooting", (DS00007).

## 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Powerup Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or Wake-up from SLEEP.

## 12.7 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100 $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

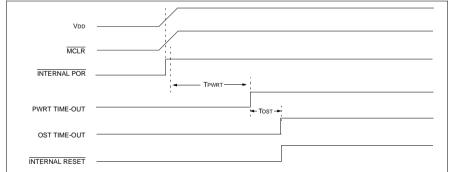

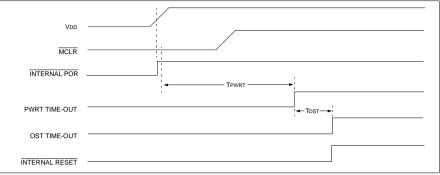

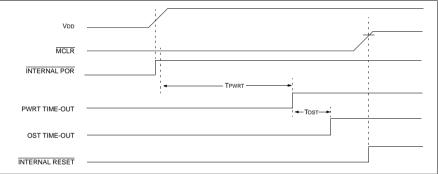

### 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: The PWRT delay starts (if enabled) when a POR Reset occurs. Then OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87X device operating in parallel.

Table 12-5 shows the RESET conditions for the STA-TUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

### 12.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit1 is  $\overline{\text{POR}}$  (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power            | -up       | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | —            |  |

## TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR    | BOR                                         | то | PD |                                                         |  |  |  |  |

|--------|---------------------------------------------|----|----|---------------------------------------------------------|--|--|--|--|

| 0      | x                                           | 1  | 1  | Power-on Reset                                          |  |  |  |  |

| 0      | х                                           | 0  | x  | Illegal, TO is set on POR                               |  |  |  |  |

| 0      | х                                           | х  | 0  | Illegal, PD is set on POR                               |  |  |  |  |

| 1      | 0                                           | 1  | 1  | Brown-out Reset                                         |  |  |  |  |

| 1      | 1                                           | 0  | 1  | WDT Reset                                               |  |  |  |  |

| 1      | 1                                           | 0  | 0  | WDT Wake-up                                             |  |  |  |  |

| 1      | 1                                           | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |

| 1      | 1                                           | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |  |

| Logond | $\log \log t = \log t \log t \log t \log t$ |    |    |                                                         |  |  |  |  |

Legend: x = don't care, u = unchanged

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

## PIC16F87X

## TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register   | Devices |     |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT of<br>Interrupt |

|------------|---------|-----|-----|-----|------------------------------------|---------------------------|---------------------------------|

| W          | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| INDF       | 873     | 874 | 876 | 877 | N/A                                | N/A                       | N/A                             |

| TMR0       | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PCL        | 873     | 874 | 876 | 877 | 0000h                              | 0000h                     | PC + 1 <sup>(2)</sup>           |

| STATUS     | 873     | 874 | 876 | 877 | 0001 1xxx                          | 000q quuu <b>(3)</b>      | uuuq quuu(3)                    |

| FSR        | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTA      | 873     | 874 | 876 | 877 | 0x 0000                            | 0u 0000                   | uu uuuu                         |

| PORTB      | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTC      | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTD      | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTE      | 873     | 874 | 876 | 877 | xxx                                | uuu                       | uuu                             |

| PCLATH     | 873     | 874 | 876 | 877 | 0 0000                             | 0 0000                    | u uuuu                          |

| INTCON     | 873     | 874 | 876 | 877 | 0000 000x                          | 0000 000u                 | uuuu uuuu(1)                    |

| PIR1       | 873     | 874 | 876 | 877 | r000 0000                          | r000 0000                 | ruuu uuuu(1)                    |

|            | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu(1)                    |

| PIR2       | 873     | 874 | 876 | 877 | -r-0 00                            | -r-0 00                   | -r-u uu <sup>(1)</sup>          |

| TMR1L      | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| TMR1H      | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| T1CON      | 873     | 874 | 876 | 877 | 00 0000                            | uu uuuu                   | uu uuuu                         |

| TMR2       | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| T2CON      | 873     | 874 | 876 | 877 | -000 0000                          | -000 0000                 | -uuu uuuu                       |

| SSPBUF     | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| SSPCON     | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| CCPR1L     | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| CCPR1H     | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| CCP1CON    | 873     | 874 | 876 | 877 | 00 0000                            | 00 0000                   | uu uuuu                         |

| RCSTA      | 873     | 874 | 876 | 877 | 0000 000x                          | 0000 000x                 | uuuu uuuu                       |

| TXREG      | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| RCREG      | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| CCPR2L     | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| CCPR2H     | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| CCP2CON    | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| ADRESH     | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| ADCON0     | 873     | 874 | 876 | 877 | 0000 00-0                          | 0000 00-0                 | uuuu uu-u                       |

| OPTION REG | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISA      | 873     | 874 | 876 | 877 | 11 1111                            | 11 1111                   | uu uuuu                         |

| TRISB      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISC      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISD      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISE      | 873     | 874 | 876 | 877 | 0000 -111                          | 0000 -111                 | uuuu -uuu                       |

| PIE1       | 873     | 874 | 876 | 877 | r000 0000                          | r000 0000                 | ruuu uuuu                       |

|            | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

```

DS30292C-page 126

```

## TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |           |           |

|----------|---------|-----|------------------------------------|---------------------------|---------------------------------|-----------|-----------|

| PIE2     | 873     | 874 | 876                                | 877                       | -r-0 00                         | -r-0 00   | -r-u uu   |

| PCON     | 873     | 874 | 876                                | 877                       | dd                              | uu        | uu        |

| PR2      | 873     | 874 | 876                                | 877                       | 1111 1111                       | 1111 1111 | 1111 1111 |

| SSPADD   | 873     | 874 | 876                                | 877                       | 0000 0000                       | 0000 0000 | uuuu uuuu |

| SSPSTAT  | 873     | 874 | 876                                | 877                       | 00 0000                         | 00 0000   | uu uuuu   |

| TXSTA    | 873     | 874 | 876                                | 877                       | 0000 -010                       | 0000 -010 | uuuu -uuu |

| SPBRG    | 873     | 874 | 876                                | 877                       | 0000 0000                       | 0000 0000 | uuuu uuuu |

| ADRESL   | 873     | 874 | 876                                | 877                       | xxxx xxxx                       | uuuu uuuu | uuuu uuuu |

| ADCON1   | 873     | 874 | 876                                | 877                       | 0 0000                          | 0 0000    | u uuuu    |

| EEDATA   | 873     | 874 | 876                                | 877                       | 0 0000                          | 0 0000    | u uuuu    |

| EEADR    | 873     | 874 | 876                                | 877                       | XXXX XXXX                       | uuuu uuuu | uuuu uuuu |

| EEDATH   | 873     | 874 | 876                                | 877                       | XXXX XXXX                       | uuuu uuuu | uuuu uuuu |

| EEADRH   | 873     | 874 | 876                                | 877                       | XXXX XXXX                       | uuuu uuuu | uuuu uuuu |

| EECON1   | 873     | 874 | 876                                | 877                       | x x000                          | u u000    | u uuuu    |

| EECON2   | 873     | 874 | 876                                | 877                       |                                 |           |           |

Legend: u =unchanged, x =unknown, - = unimplemented bit, read as '0', q = value depends on condition, r =reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

## FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

## PIC16F87X

## FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

## FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

## FIGURE 12-8: SLOW RISE TIME (MCLR TIED TO VDD)

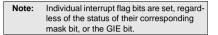

#### 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

#### FIGURE 12-9: INTERRUPT LOGIC

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

## PIC16F87X

#### 12.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG-6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 for details on SLEEP mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON-0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 3.2).

### EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS, W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS TEMP    | ;Save status to bank zero STATUS TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| :      |                |                                                         |

| :(ISR) |                | ; (Insert user code here)                               |

| :      |                |                                                         |

| MOVF   | PCLATH TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS TEMP,W  | ;Swap STATUS TEMP register into W                       |

|        |                | ; (sets bank to original state)                         |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W TEMP,F       | ;Swap W TEMP                                            |

| SWAPF  | W TEMP,W       | ;Swap W TEMP into W                                     |

|        |                |                                                         |

## 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

For the PIC16F873/874 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F876/877 devices, temporary holding registers W\_TEMP, STATUS\_TEMP, and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

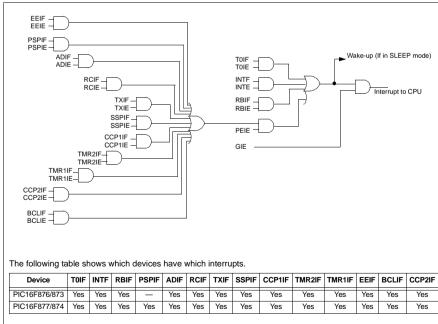

### 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 12.1).

#### FIGURE 12-10: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

### WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned

Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

using the OPTION REG register.

When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## PIC16F87X

### 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

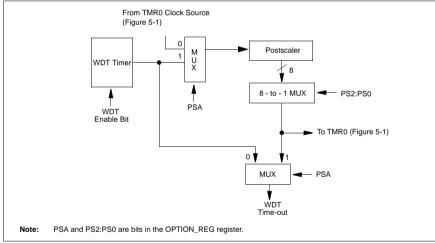

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External  $\overline{\text{MCLR}}$  Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device RESET. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when <code>SLEEP</code> is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present. When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overrightarrow{PD}$  bit. If the  $\overrightarrow{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### FIGURE 12-11: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP oscillator mode assumed.

TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

GIE = '1' assumed. In this case, after wake- up, the processor jumps to the interrupt routine

If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

### 12.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLA® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-8 shows which features are consumed by the background debugger.

### TABLE 12-8: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7                                     |

|----------------|----------------------------------------------|

| Stack          | 1 level                                      |

| Program Memory | Address 0000h must be NOP                    |

|                | Last 100h words                              |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB - 0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies.

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

### 12.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

## PIC16F87X

### 12.17 In-Circuit Serial Programming

PIC16F87X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

## 12.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87X device will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.