# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- · 8-bit timer/counter

- · Readable and writable

- · 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- · Edge select for external clock

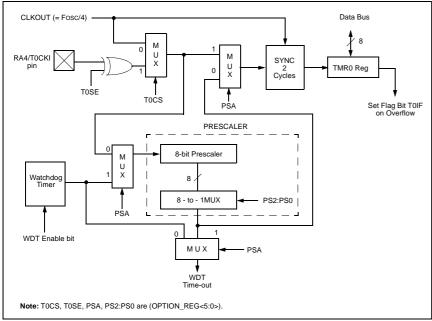

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit T0CS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TOIF (INTCON<2>). The interrupt can be masked by clearing bit TOIE (INTCON<5>). Bit TOIF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

## FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

## REGISTER 5-1: OPTION\_REG REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

readable or writable.

Timer0 module means that there is no prescaler for the

Watchdog Timer, and vice-versa. This prescaler is not

The PSA and PS2:PS0 bits (OPTION REG<3:0>)

determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions

writing to the TMR0 register (e.g. CLRF1, MOVWF1,

BSF 1, x....etc.) will clear the prescaler. When assigned

to WDT, a CLRWDT instruction will clear the prescaler

along with the Watchdog Timer. The prescaler is not

Note: Writing to TMR0, when the prescaler is

assigned to Timer0, will clear the prescaler

count, but will not change the prescaler

readable or writable (see Figure 5-1).

assignment.

- bit 7 RBPU

- bit 6 INTEDG

- bit 5 **TOCS**: TMR0 Clock Source Select bit 1 = Transition on T0CKI pin 0 = Internal instruction cycle clock (CLKOUT)

- bit 4 **T0SE**: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

- bit 3 **PSA**: Prescaler Assignment bit 1 = Prescaler is assigned to the WDT 0 = Prescaler is assigned to the Timer0 module

- bit 2-0 PS2:PS0: Prescaler Rate Select bits

Bit Value TMR0 Rate WDT Rate

| 000 | 1:2   | 1:1   |

|-----|-------|-------|

| 001 | 1:4   | 1:2   |

| 010 | 1:8   | 1:4   |

| 011 | 1:16  | 1:8   |

| 100 | 1:32  | 1:16  |

| 101 | 1:64  | 1:32  |

| 110 | 1:128 | 1:64  |

| 111 | 1:256 | 1:128 |

|     |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Note: To avoid an unintended device RESET, the instruction sequence shown in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

# TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7  | Bit 6                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|------------|--------|--------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 | Timer0 Module's Register |       |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE                     | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG                   | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as ' 0' . Shaded cells are not used by Timer0.

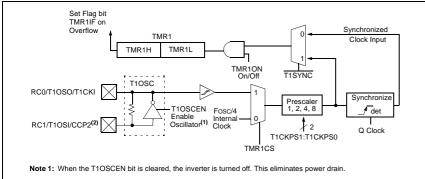

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023).

# REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |  |

|-------|-----|---------|---------|---------|--------|--------|--------|--|

| _     |     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |  |

| bit 7 |     |         |         |         |        |        | bit 0  |  |

- bit 7-6 Unimplemented: Read as ' 0'

- bit 5-4 T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits

- 11 = 1:8 Prescale value

- 10 = 1:4 Prescale value

- 01 = 1:2 Prescale value

- 00 = 1:1 Prescale value

- bit 3 T1OSCEN: Timer1 Oscillator Enable Control bit

- 1 = Oscillator is enabled

- 0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain)

- T1SYNC: Timer1 External Clock Input Synchronization Control bit

- When TMR1CS = 1:

bit 2

bit 1

- 1 = Do not synchronize external clock input

- 0 = Synchronize external clock input

- When TMR1CS = 0:

- This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

- TMR1CS: Timer1 Clock Source Select bit

- 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

- bit 0 **TMR10N**: Timer1 On bit

- 0 = Stops Timer1

#### Legend.

| Legend.            |                  |                      |                    |  |

|--------------------|------------------|----------------------|--------------------|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | pit, read as '0'   |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit TISYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

#### 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous, or an Asynchronous mode, depending on the setting of the TMR1CS bit.

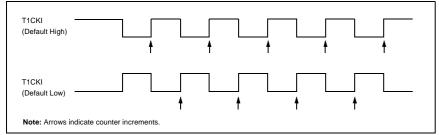

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### FIGURE 6-1: TIMER1 INCREMENTING EDGE

#### 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

# Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external

clock input is not synchronized. The timer continues to

increment asynchronous to the internal phase clocks.

The timer will continue to run during SLEEP and can

generate an interrupt-on-overflow, which will wake-up

the processor. However, special precautions in soft-

ware are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare opera-

READING AND WRITING TIMER1 IN

ASYNCHRONOUS COUNTER

Reading TMR1H or TMR1L while the timer is running

from an external asynchronous clock, will guarantee a

valid read (taken care of in hardware). However, the

user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since

For writes, it is recommended that the user simply stop

the timer and write the desired values. A write conten-

tion may occur by writing to the timer registers, while

the register is incrementing. This may produce an

Reading the 16-bit value requires some care. Exam-

ples 12-2 and 12-3 in the PICmicro™ Mid-Range MCU

Family Reference Manual (DS33023) show how to

read and write Timer1 when it is running in Asynchro-

A crystal oscillator circuit is built-in between pins T1OSI

(input) and T1OSO (amplifier output). It is enabled by

setting control bit T1OSCEN (T1CON<3>). The oscilla-

tor is a low power oscillator, rated up to 200 kHz. It will

continue to run during SLEEP. It is primarily intended

for use with a 32 kHz crystal. Table 6-1 shows the

The Timer1 oscillator is identical to the LP oscillator.

The user must provide a software time delay to ensure

the timer may overflow between the reads.

unpredictable value in the timer register.

Timer1 Oscillator

capacitor selection for the Timer1 oscillator.

proper oscillator start-up.

6.4

tions.

6.4.1

nous mode.

6.5

MODE

TABLE 6-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                                   | Freq.                                                                                                    | C1                                                    | C2                                        |  |  |  |  |  |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------|--|--|--|--|--|--|--|

| LP                                         | 32 kHz                                                                                                   | 33 pF                                                 | 33 pF                                     |  |  |  |  |  |  |  |

|                                            | 100 kHz                                                                                                  | 15 pF                                                 | 15 pF                                     |  |  |  |  |  |  |  |

|                                            | 200 kHz                                                                                                  | 15 pF                                                 | 15 pF                                     |  |  |  |  |  |  |  |

| These values are for design guidance only. |                                                                                                          |                                                       |                                           |  |  |  |  |  |  |  |

| Crystals Tested:                           |                                                                                                          |                                                       |                                           |  |  |  |  |  |  |  |

| 32.768 kH                                  | z Epson C-0                                                                                              | 01R32.768K-A                                          | ± 20 PPM                                  |  |  |  |  |  |  |  |

| 100 kHz                                    | Epson C-2                                                                                                | Epson C-2 100.00 KC-P ± 20 PI                         |                                           |  |  |  |  |  |  |  |

| 200 kHz                                    | STD XTL                                                                                                  | 200.000 kHz                                           | ± 20 PPM                                  |  |  |  |  |  |  |  |

| 2: S                                       | Higher capacita<br>of oscillator, but<br>ime.<br>Since each reso<br>characteristics,<br>resonator/crysta | also increases<br>onator/crystal h<br>the user should | the start-up<br>as its own<br>consult the |  |  |  |  |  |  |  |

resonator/crystal manufacturer for appro priate values of external components.

#### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | and CCP2 modules will not set interrupt  |  |  |  |  |  |  |  |

|       | flag bit TMR1IF (PIR1<0>).               |  |  |  |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

© 2001 Microchip Technology Inc.

# 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

# 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

# TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6                                                                      | Bit 5        | Bit 4         | Bit 3         | Bit 2     | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------------------------------------------------------------------------|--------------|---------------|---------------|-----------|--------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  |                                                                            |              |               |               |           |        |           |                          | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | IF <sup>(1)</sup> ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF                |              |               |               |           |        | 0000 0000 | 0000 0000                |                                 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | PSPIE <sup>(1)</sup> ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE             |              |               |               |           |        |           | 0000 0000                | 0000 0000                       |

| 0Eh                    | TMR1L  | Holding R            | egister for th                                                             | ne Least Sig | nificant Byte | of the 16-bit | TMR1 Regi | ster   |           | XXXX XXXX                | uuuu uuuu                       |

| 0Fh                    | TMR1H  | Holding R            | lolding Register for the Most Significant Byte of the 16-bit TMR1 Register |              |               |               |           |        |           |                          | uuuu uuuu                       |

| 10h                    | T1CON  | _                    | _                                                                          | T1CKPS1      | T1CKPS0       | T10SCEN       | T1SYNC    | TMR1CS | TMR10N    | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as ' 0'. Shaded cells are not used by the Timer1 module. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

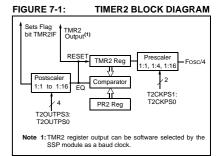

# 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4, or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>), to minimize power consumption.

Register 7-1 shows the Timer2 control register.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

## REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

|         | U-0                  | R/W-0        | R/W-0       | R/W-0        | R/W-0         | R/W-0     | R/W-0        | R/W-0   |  |  |  |  |  |

|---------|----------------------|--------------|-------------|--------------|---------------|-----------|--------------|---------|--|--|--|--|--|

|         | —                    | TOUTPS3      | TOUTPS2     | TOUTPS1      | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |  |  |  |  |  |

|         | bit 7                |              |             |              |               |           |              | bit 0   |  |  |  |  |  |

|         |                      |              |             |              |               |           |              |         |  |  |  |  |  |

| bit 7   | Unimplen             | nented: Rea  | d as '0'    |              |               |           |              |         |  |  |  |  |  |

| bit 6-3 | TOUTPS3              | :TOUTPS0:    | Timer2 Out  | put Postsca  | e Select bits |           |              |         |  |  |  |  |  |

|         | 0000 = 1:1 Postscale |              |             |              |               |           |              |         |  |  |  |  |  |

|         | 0001 = 1:            | 2 Postscale  |             |              |               |           |              |         |  |  |  |  |  |

|         | 0010 = 1:            | 3 Postscale  |             |              |               |           |              |         |  |  |  |  |  |

|         | •                    |              |             |              |               |           |              |         |  |  |  |  |  |

|         | •                    |              |             |              |               |           |              |         |  |  |  |  |  |

|         | •                    |              |             |              |               |           |              |         |  |  |  |  |  |

|         |                      | 16 Postscale |             |              |               |           |              |         |  |  |  |  |  |

| bit 2   | TMR2ON:              | Timer2 On I  | oit         |              |               |           |              |         |  |  |  |  |  |

|         | 1 = Timer2           |              |             |              |               |           |              |         |  |  |  |  |  |

|         | 0 = Timer2           | 2 is off     |             |              |               |           |              |         |  |  |  |  |  |

| bit 1-0 | T2CKPS1              | :T2CKPS0:    | Timer2 Cloc | k Prescale   | Select bits   |           |              |         |  |  |  |  |  |

|         | 00 = Pres            | caler is 1   |             |              |               |           |              |         |  |  |  |  |  |

|         | 01 = Pres            | caler is 4   |             |              |               |           |              |         |  |  |  |  |  |

|         | 1x = Pres            | caler is 16  |             |              |               |           |              |         |  |  |  |  |  |

|         |                      |              |             |              |               |           |              |         |  |  |  |  |  |

|         | Legend:              |              |             |              |               |           |              |         |  |  |  |  |  |

|         | R = Read             | able bit     | W = V       | Vritable bit | U = Unim      | plemented | bit, read as | '0'     |  |  |  |  |  |

|  | - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|--|--------------------|------------------|----------------------|--------------------|

|--|--------------------|------------------|----------------------|--------------------|

#### 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset, or BOR)

TMR2 is not cleared when T2CON is written.

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address               | Name   | Bit 7                | Bit 6                   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|--------|----------------------|-------------------------|---------|---------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                    | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 Mod           | imer2 Module's Register |         |         |         |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  |                      | TOUTPS3                 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri          | od Register             |         |         |         |        |         |         | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as ' 0'. Shaded cells are not used by the Timer2 module. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

# 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

# 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

# CCP1 Module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1.

# CCP2 Module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PICmicro™ Mid-Range MCU Family Reference Manual (DS33023) and in application note AN594, "Using the CCP Modules" (DS00594).

# TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode           | Timer Resource   |

|--------------------|------------------|

| Capture<br>Compare | Timer1<br>Timer1 |

| PWM                | Timer2           |

# TABLE 8-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                          |

|-----------|-----------|--------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1 |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt)               |

| PWM       | Capture   | None                                                                                 |

| PWM       | Compare   | None                                                                                 |

| REGISTER 8-1: | CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)                                                                                         |                                                                                                        |                              |              |                                    |        |        |        |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------|--------------|------------------------------------|--------|--------|--------|--|--|--|--|--|--|

|               | U-0                                                                                                                                          | U-0                                                                                                    | R/W-0                        | R/W-0        | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |  |  |  |  |  |

|               | _                                                                                                                                            | —                                                                                                      | CCPxX                        | CCPxY        | CCPxM3                             | CCPxM2 | CCPxM1 | CCPxM0 |  |  |  |  |  |  |

|               | bit 7                                                                                                                                        |                                                                                                        |                              |              |                                    |        |        | bit 0  |  |  |  |  |  |  |

| bit 7-6       | Unimplem                                                                                                                                     | ented: Rea                                                                                             | ad as '0'                    |              |                                    |        |        |        |  |  |  |  |  |  |

| bit 5-4       | CCPxX:CC                                                                                                                                     | CPxY: PWM                                                                                              | I Least Sign                 | ificant bits |                                    |        |        |        |  |  |  |  |  |  |

|               | Capture me<br>Unused                                                                                                                         | Capture mode:<br>Unused                                                                                |                              |              |                                    |        |        |        |  |  |  |  |  |  |

|               | <u>Compare mode:</u><br>Unused<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL. |                                                                                                        |                              |              |                                    |        |        |        |  |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                        |                              |              |                                    |        |        |        |  |  |  |  |  |  |

| bit 3-0       | CCPxM3:0                                                                                                                                     | CPxM0: C                                                                                               | CPx Mode S                   | Select bits  |                                    |        |        |        |  |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                        |                              |              | ets CCPx mo                        | dule)  |        |        |  |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                        | , every fallir               |              |                                    |        |        |        |  |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                        | , every risin<br>, every 4th |              |                                    |        |        |        |  |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                        |                              | rising edge  |                                    |        |        |        |  |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                        |                              |              | CCPxIF bit is                      |        |        |        |  |  |  |  |  |  |

|               |                                                                                                                                              |                                                                                                        |                              |              | n (CCPxIF bit                      |        |        |        |  |  |  |  |  |  |

|               | una                                                                                                                                          | 10 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is<br>unaffected) |                              |              |                                    |        |        |        |  |  |  |  |  |  |

|               | res                                                                                                                                          |                                                                                                        |                              |              | CCPxIF bit is s<br>I starts an A/E |        |        |        |  |  |  |  |  |  |

|               | 11xx = PW                                                                                                                                    | /M mode                                                                                                |                              |              |                                    |        |        |        |  |  |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

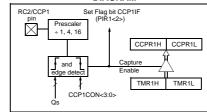

## 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

The type of event is configured by control bits CCP1M3:CCP1M0 (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new value.

8.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

Note: If the RC2/CCP1 pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF, following any such change in operating mode.

# 8.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

| EXAMF         |                        | HANGING BETWEEN                                                       |

|---------------|------------------------|-----------------------------------------------------------------------|

| CLRF<br>MOVLW | CCP1CON<br>NEW_CAPT_PS | ; Turn CCP module off<br>; Load the W reg with<br>; the new prescaler |

| MOVWF         | CCP1CON                | ; move value and CCP ON<br>; Load CCP1CON with this<br>; value        |

### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

reset Timer1, but not set interrupt flag bit TMR1IF (PIR1<0>), and set bit GO/DONE (ADCON0<2>). Special Event Trigger Set Flag bit CCP1IF (PIR1<2>) CCPR1H CCPR1L Uogic TRISC<2>, Output Enable CCP1CON<3:0> Mode Select

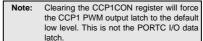

# 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force<br>the RC2/CCP1 compare output latch to the |

|-------|--------------------------------------------------------------------------------------|

|       | default low level. This is not the PORTC I/O data latch.                             |

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

## 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

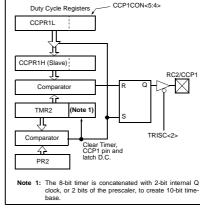

# 8.3 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 8.3.3.

FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

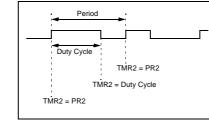

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 8-4: PWM OUTPUT

# 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$  (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

- Note: The Timer2 postscaler (see Section 7.1) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

# 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

PWM duty cycle =(CCPR1L:CCP1CON<5:4>) • TOSC • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitch-free PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock, or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

## 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

# TABLE 8-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7                | Bit 6                                   | Bit 5         | Bit 4         | Bit 3         | Bit 2      | Bit 1    | Bit 0  | Value<br>POF<br>BO | ٦,   | all o | e on<br>other<br>SETS |

|------------------------|---------|----------------------|-----------------------------------------|---------------|---------------|---------------|------------|----------|--------|--------------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                    | TOIE          | INTE          | RBIE          | TOIF       | INTF     | RBIF   | 0000 (             | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                    | RCIF          | TXIF          | SSPIF         | CCP1IF     | TMR2IF   | TMR1IF | 0000               | 0000 | 0000  | 0000                  |

| 0Dh                    | PIR2    | _                    | —                                       | -             | _             | -             | -          |          | CCP2IF |                    | 0    |       | 0                     |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                    | RCIE          | TXIE          | SSPIE         | CCP1IE     | TMR2IE   | TMR1IE | 0000               | 0000 | 0000  | 0000                  |

| 8Dh                    | PIE2    | _                    | -                                       | -             | -             |               |            | -        | CCP2IE |                    | 0    |       | 0                     |

| 87h                    | TRISC   | PORTC D              | ata Direc                               | tion Registe  | r             |               |            |          |        | 1111 :             | 1111 | 1111  | 1111                  |

| 0Eh                    | TMR1L   | Holding R            | egister for                             | r the Least S | Significant E | Byte of the 1 | 6-bit TMR1 | Register |        | XXXX 2             | xxxx | uuuu  | uuuu                  |

| 0Fh                    | TMR1H   | Holding R            | egister for                             | r the Most S  | ignificant B  | yte of the 16 | 6-bit TMR1 | Register |        | XXXX 3             | xxxx | uuuu  | uuuu                  |

| 10h                    | T1CON   | _                    | -                                       | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS   | TMR10N | 00 (               | 0000 | uu    | uuuu                  |

| 15h                    | CCPR1L  | Capture/C            | Compare/F                               | PWM Regist    | er1 (LSB)     |               |            |          |        | XXXX 2             | xxxx | uuuu  | uuuu                  |

| 16h                    | CCPR1H  | Capture/C            | Compare/F                               | PWM Regist    | er1 (MSB)     |               |            |          |        | XXXX 2             | xxxx | uuuu  | uuuu                  |

| 17h                    | CCP1CON | —                    | CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0 |               |               |               |            |          |        | 00 (               | 0000 | 00    | 0000                  |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB)     |               |               |               |            |          |        | XXXX 2             | xxxx | uuuu  | uuuu                  |

| 1Ch                    | CCPR2H  | Capture/C            | compare/F                               | PWM Regist    | er2 (MSB)     |               |            |          |        | XXXX 3             | xxxx | uuuu  | uuuu                  |

| 1Dh                    | CCP2CON | _                    | -                                       | CCP2X         | CCP2Y         | CCP2M3        | CCP2M2     | CCP2M1   | CCP2M0 | 00 (               | 0000 | 00    | 0000                  |

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

# TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address                | Name    | Bit 7                | Bit 6         | Bit 5       | Bit 4       | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | : Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|---------------|-------------|-------------|---------|--------|---------|---------|-------------------------|-----------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE          | TOIE        | INTE        | RBIE    | TOIF   | INTF    | RBIF    | 0000 000                | x 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF        | TXIF        | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 000                | 0 0000 0000                       |

| 0Dh                    | PIR2    | _                    | —             | _           | —           | -       | -      | —       | CCP2IF  |                         | 0 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE        | TXIE        | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 000                | 0 0000 0000                       |

| 8Dh                    | PIE2    | _                    | —             | _           | —           | -       | -      | —       | CCP2IE  |                         | 0 0                               |

| 87h                    | TRISC   | PORTC [              | Data Directio | n Register  |             |         |        |         |         | 1111 111                | .1 1111 1111                      |

| 11h                    | TMR2    | Timer2 M             | odule's Regi  | ister       |             |         |        |         |         | 0000 000                | 0 0000 0000                       |

| 92h                    | PR2     | Timer2 M             | odule's Perio | od Register |             |         |        |         |         | 1111 111                | .1 1111 1111                      |

| 12h                    | T2CON   |                      | TOUTPS3       | TOUTPS2     | TOUTPS1     | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 000                | 0 -000 0000                       |

| 15h                    | CCPR1L  | Capture/0            | Compare/PV    | /M Register | 1 (LSB)     |         |        |         |         | хххх ххэ                | x uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/0            | Compare/PV    | /M Register | 1 (MSB)     |         |        |         |         | XXXX XXX                | x uuuu uuuu                       |

| 17h                    | CCP1CON |                      | _             | CCP1X       | CCP1Y       | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 000                  | 000 0000                          |

| 1Bh                    | CCPR2L  | Capture/0            | Compare/PV    | XXXX XXX    | x uuuu uuuu |         |        |         |         |                         |                                   |

| 1Ch                    | CCPR2H  | Capture/0            | Compare/PW    | /M Register | 2 (MSB)     |         |        |         |         | хххх ххо                | x uuuu uuuu                       |

| 1Dh                    | CCP2CON | _                    | -             | CCP2X       | CCP2Y       | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00 000                  | 000 0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as ' 0' . Shaded cells are not used by PWM and Timer2. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.