# 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, serial EEPROMS etc.

The USART can be configured in the following modes:

- Asynchronous (full duplex)

- · Synchronous Master (half duplex)

- · Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R-1  | R/W-0 |

|---|-------|-------|-------|-------|-----|-------|------|-------|

| ſ | CSRC  | TX9   | TXEN  | SYNC  | _   | BRGH  | TRMT | TX9D  |

|   | hit 7 |       |       |       |     |       |      | hit ∩ |

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Don't care

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 TX9: 9-bit Transmit Enable bit

1 = Selects 9-bit transmission

0 = Selects 8-bit transmission

bit 5 TXEN: Transmit Enable bit

1 = Transmit enabled

0 = Transmit disabled

Note: SREN/CREN overrides TXEN in SYNC mode.

bit 4 SYNC: USART Mode Select bit

1 = Synchronous mode

0 = Asynchronous mode

bit 3 Unimplemented: Read as ' 0'

bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode

bit 1 TRMT: Transmit Shift Register Status bit

1 = TSR empty

0 = TSR full

bit 0 TX9D: 9th bit of Transmit Data, can be parity bit

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

© 2001 Microchip Technology Inc. DS30292C-page 95

### PIC16F87X

#### REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0  | R-0  | R-x   |

|-------|-------|-------|-------|-------|------|------|-------|

| SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR | OERR | RX9D  |

| bit 7 |       |       |       |       |      |      | bit 0 |

bit 7 SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RC7/RX/DT and RC6/TX/CK pins as serial port pins)

0 = Serial port disabled

bit 6 RX9: 9-bit Receive Enable bit

1 = Selects 9-bit reception

0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Don't care

Synchronous mode - master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - slave:

Don't care

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables continuous receive

0 = Disables continuous receive

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enables interrupt and load of the receive buffer when

RSR<8> is set

0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit

bit 2 FERR: Framing Error bit

1 = Framing error (can be updated by reading RCREG register and receive next valid byte)

0 = No framing error

bit 1 OERR: Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 RX9D: 9th bit of Received Data (can be parity bit, but must be calculated by user firmware)

Legend:

$R = Readable \ bit \qquad \qquad W = Writable \ bit \qquad \qquad U = Unimplemented \ bit, \ read \ as \ '0' \\ -n = Value \ at \ POR \qquad \qquad '1' = Bit \ is \ set \qquad '0' = Bit \ is \ cleared \qquad x = Bit \ is \ unknown$

DS30292C-page 96 © 2001 Microchip Technology Inc.

# 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7   | Bit 6                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|---------|----------------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA | CSRC    | TX9                                    | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA | SPEN    | PEN RX9 SREN CREN ADDEN FERR OERR RX9D |       |       |       |       |       | RX9D  | 0000 000x                | 0000 000x                       |

| 99h     | SPBRG | Baud Ra | aud Rate Generator Register            |       |       |       |       |       |       |                          | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0' . Shaded cells are not used by the BRG.

© 2001 Microchip Technology Inc. DS30292C-page 97

# PIC16F87X

#### TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | F       | osc = 20 N | lHz                         | F       | osc = 16 N | lHz                         | ı       | osc = 10 N | ИНz                         |

|-------------|---------|------------|-----------------------------|---------|------------|-----------------------------|---------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         |         | -          | -                           | -       | -          | -                           | -       | -          | -                           |

| 1.2         | 1.221   | 1.75       | 255                         | 1.202   | 0.17       | 207                         | 1.202   | 0.17       | 129                         |

| 2.4         | 2.404   | 0.17       | 129                         | 2.404   | 0.17       | 103                         | 2.404   | 0.17       | 64                          |

| 9.6         | 9.766   | 1.73       | 31                          | 9.615   | 0.16       | 25                          | 9.766   | 1.73       | 15                          |

| 19.2        | 19.531  | 1.72       | 15                          | 19.231  | 0.16       | 12                          | 19.531  | 1.72       | 7                           |

| 28.8        | 31.250  | 8.51       | 9                           | 27.778  | 3.55       | 8                           | 31.250  | 8.51       | 4                           |

| 33.6        | 34.722  | 3.34       | 8                           | 35.714  | 6.29       | 6                           | 31.250  | 6.99       | 4                           |

| 57.6        | 62.500  | 8.51       | 4                           | 62.500  | 8.51       | 3                           | 52.083  | 9.58       | 2                           |

| HIGH        | 1.221   | -          | 255                         | 0.977   | -          | 255                         | 0.610   | -          | 255                         |

| LOW         | 312.500 | -          | 0                           | 250.000 | -          | 0                           | 156.250 | -          | 0                           |

| BAUD        | 1      | Fosc = 4 M | Hz                          | Fo    | sc = 3.6864 | MHz                         |

|-------------|--------|------------|-----------------------------|-------|-------------|-----------------------------|

| RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR  | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300  | 0          | 207                         | 0.3   | 0           | 191                         |

| 1.2         | 1.202  | 0.17       | 51                          | 1.2   | 0           | 47                          |

| 2.4         | 2.404  | 0.17       | 25                          | 2.4   | 0           | 23                          |

| 9.6         | 8.929  | 6.99       | 6                           | 9.6   | 0           | 5                           |

| 19.2        | 20.833 | 8.51       | 2                           | 19.2  | 0           | 2                           |

| 28.8        | 31.250 | 8.51       | 1                           | 28.8  | 0           | 1                           |

| 33.6        | -      | -          | -                           | -     | -           | -                           |

| 57.6        | 62.500 | 8.51       | 0                           | 57.6  | 0           | 0                           |

| HIGH        | 0.244  | -          | 255                         | 0.225 | -           | 255                         |

| LOW         | 62.500 | -          | 0                           | 57.6  | -           | 0                           |

#### TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

|                     |          |            |                             |          |            |                             |               |            | -                           |  |

|---------------------|----------|------------|-----------------------------|----------|------------|-----------------------------|---------------|------------|-----------------------------|--|

|                     | F        | osc = 20 M | Hz                          | F        | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |  |

| BAUD<br>RATE<br>(K) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | -        | -          | -                           | -        | -          | -                           | -             | -          | -                           |  |

| 1.2                 | -        | -          | -                           | -        | -          | -                           | -             | -          | -                           |  |

| 2.4                 | -        | -          | -                           | -        | -          | -                           | 2.441         | 1.71       | 255                         |  |

| 9.6                 | 9.615    | 0.16       | 129                         | 9.615    | 0.16       | 103                         | 9.615         | 0.16       | 64                          |  |

| 19.2                | 19.231   | 0.16       | 64                          | 19.231   | 0.16       | 51                          | 19.531        | 1.72       | 31                          |  |

| 28.8                | 29.070   | 0.94       | 42                          | 29.412   | 2.13       | 33                          | 28.409        | 1.36       | 21                          |  |

| 33.6                | 33.784   | 0.55       | 36                          | 33.333   | 0.79       | 29                          | 32.895        | 2.10       | 18                          |  |

| 57.6                | 59.524   | 3.34       | 20                          | 58.824   | 2.13       | 16                          | 56.818        | 1.36       | 10                          |  |

| HIGH                | 4.883    | -          | 255                         | 3.906    | -          | 255                         | 2.441         | -          | 255                         |  |

| LOW                 | 1250.000 | -          | 0                           | 1000.000 |            | 0                           | 625.000       | -          | 0                           |  |

| BAUD        | F       | osc = 4 MH | łz                          | Fosc = 3.6864 MHz |            |                             |  |  |  |

|-------------|---------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3         | -       | -          | -                           | -                 | -          | -                           |  |  |  |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2               | 0          | 191                         |  |  |  |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4               | 0          | 95                          |  |  |  |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6               | 0          | 23                          |  |  |  |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2              | 0          | 11                          |  |  |  |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8              | 0          | 7                           |  |  |  |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9              | 2.04       | 6                           |  |  |  |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6              | 0          | 3                           |  |  |  |

| HIGH        | 0.977   | -          | 255                         | 0.9               | -          | 255                         |  |  |  |

| LOW         | 250.000 | -          | 0                           | 230.4             | -          | 0                           |  |  |  |

DS30292C-page 98 © 2001 Microchip Technology Inc.

#### 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-to-zero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

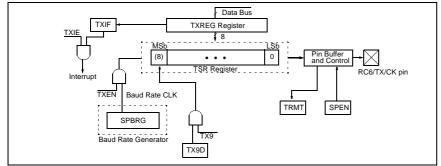

# 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcv), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

Note 1: The TSR register is not mapped in data memory, so it is not available to the user.

2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

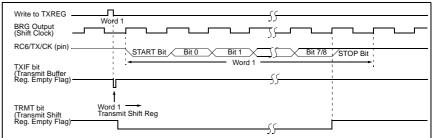

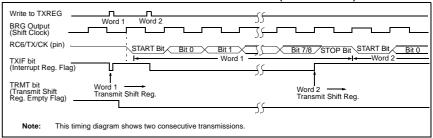

Transmission is enabled by setting enable bit TXEN (TXSTA-5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA-6>) should be set and the ninth bit should be written to TX9D (TXSTA-<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

© 2001 Microchip Technology Inc. DS30292C-page 99

# PIC16F87X

When setting up an Asynchronous Transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|------------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE       | INTE  | RBIE      | TOIF      | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN       | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | nsmit Re | gister     |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN       | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato | r Register |       | 0000 0000 | 0000 0000 |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

DS30292C-page 100 © 2001 Microchip Technology Inc.

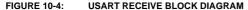

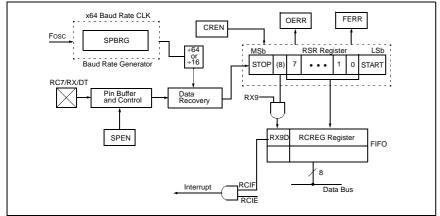

# 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

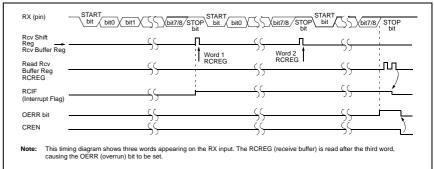

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It

is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited. and no further data will be received. It is therefore. essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

© 2001 Microchip Technology Inc. DS30292C-page 101

# PIC16F87X

#### FIGURE 10-5: ASYNCHRONOUS RECEPTION

When setting up an Asynchronous Reception, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

- If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6                                                         | Bit 5      | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|---------------------------------------------------------------|------------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                                          | TOIE       | INTE  | RBIE      | TOIF      | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                          | RCIF       | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                                                           | SREN       | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART F              | Receive Reg                                                   | gister     |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | SPIE <sup>(1)</sup> ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE |            |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                                                           | TXEN       | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rat             | e Generato                                                    | r Register |       | 0000 0000 | 0000 0000 |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

DS30292C-page 102 © 2001 Microchip Technology Inc.

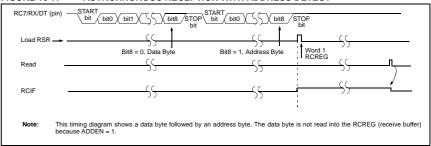

# 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- . If interrupts are desired, then set enable bit RCIE.

- · Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

© 2001 Microchip Technology Inc. DS30292C-page 103

# PIC16F87X

DS30292C-page 104

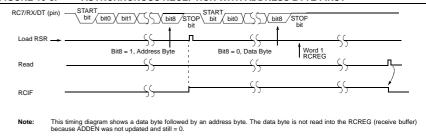

#### FIGURE 10-7: ASYNCHRONOUS RECEPTION WITH ADDRESS DETECT

#### FIGURE 10-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 10-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6                                  | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------------------------------------|--------|-----------|-----------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | GIE PEIE TOIE INTE RBIE TOIF INTF ROIF |        |           |           |        |        |        |                          | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                   | RCIF   | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                                    | SREN   | CREN      | ADDEN     | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART Re             | ceive Re                               | gister |           |           |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                   | RCIE   | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                                    | TXEN   | SYNC      | _         | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato                               |        | 0000 0000 | 0000 0000 |        |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

© 2001 Microchip Technology Inc.

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

#### 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA-4>). In addition, enable bit SPEN (RCSTA-7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA-7>).

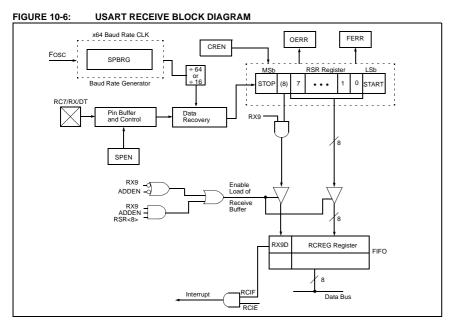

# 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-6. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

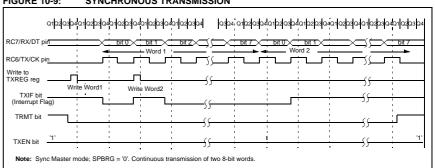

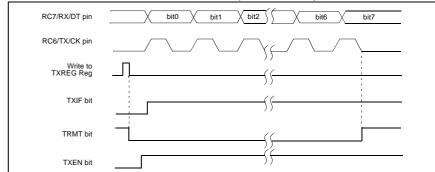

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-10). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG, Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from hiimpedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA-6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA-0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

© 2001 Microchip Technology Inc. DS30292C-page 105

### PIC16F87X

TABLE 10-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5     | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|-----------|-----------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TOIE      | INTE  | RBIE      | TOIF      | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF      | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN      | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr             | ansmit Re | egister   |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE      | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN      | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat   | or Regist |       | 0000 0000 | 0000 0000 |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

FIGURE 10-9: SYNCHRONOUS TRANSMISSION

#### FIGURE 10-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

DS30292C-page 106 © 2001 Microchip Technology Inc.

# 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

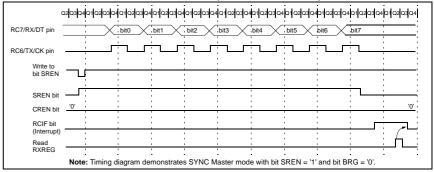

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit. the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth

receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |  |

|------------------------|--------|----------------------|-----------|-----------|-----------|-------|--------|--------|--------|--------------------------|---------------------------------|--|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TOIE      | INTE      | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |  |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN      | CREN      | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |  |

| 1Ah                    | RCREG  | USART R              | eceive Re | 0000 0000 | 0000 0000 |       |        |        |        |                          |                                 |  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |  |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN      | SYNC      | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |  |

| 99h                    | SPBRG  | Baud Rate            | e Generat | 0000 0000 | 0000 0000 |       |        |        |        |                          |                                 |  |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

© 2001 Microchip Technology Inc. DS30292C-page 107

# PIC16F87X

FIGURE 10-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

#### 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- Enable the transmission by setting enable bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on all other RESETS |  |

|------------------------|--------|----------------------|----------|-----------|-----------|-------|--------|--------|--------|-----------------------|---------------------------|--|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE      | INTE      | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                 |  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                 |  |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN      | CREN      | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                 |  |

| 19h                    | TXREG  | USART Tr             | ansmit R | 0000 0000 | 0000 0000 |       |        |        |        |                       |                           |  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                 |  |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN      | SYNC      | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                 |  |

| 99h                    | SPBRG  | Baud Rate            | Generat  | 0000 0000 | 0000 0000 |       |        |        |        |                       |                           |  |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

DS30292C-page 108 © 2001 Microchip Technology Inc.

# 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don' t care in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### TABLE 10-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address                | Name   | Bit 7                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR |      | Value on all<br>other<br>RESETS |      |

|------------------------|--------|------------------------------|-------|-------|-------|-------|--------|--------|--------|--------------------------|------|---------------------------------|------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                          | PEIE  | TOIE  | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000                     | 000x | 0000                            | 000u |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>         | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000                     | 0000 | 0000                            | 0000 |

| 18h                    | RCSTA  | SPEN                         | RX9   | SREN  | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000                     | x000 | 0000                            | 000x |

| 1Ah                    | RCREG  | USART R                      | 0000  | 0000  | 0000  | 0000  |        |        |        |                          |      |                                 |      |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>         | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000                     | 0000 | 0000                            | 0000 |

| 98h                    | TXSTA  | CSRC                         | TX9   | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -                   | -010 | 0000                            | -010 |

| 99h                    | SPBRG  | Baud Rate Generator Register |       |       |       |       |        |        |        |                          | 0000 | 0000                            | 0000 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

© 2001 Microchip Technology Inc. DS30292C-page 109

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices, always maintain these bits clear.