| Version 7 (modified by , 17 years ago) (diff) |

|---|

TP4-3 : Vérification temporelle

3.1 Introduction

Ce TP aborde les contraintes de stabilité de type setup time et hold time à respecter sur les entrées externes d'un petit circuit avec un point mémorisant.

Le but de ce TP est de présenter les différences qu'il y a entre un simulateur électrique (précision, travail avec des stimuli, lenteur) et un analyseur temporel (moins précis, pas de stimuli, rapidité).

3.2 Etude de stabilité

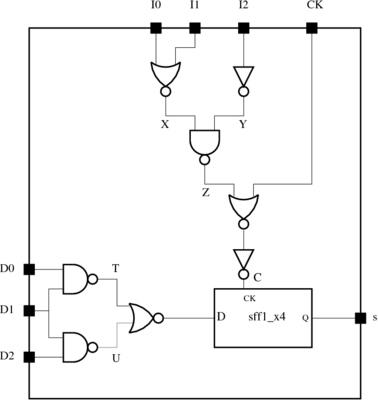

On cherche à déterminer les contraintes setup time et hold time sur les entrées dans le cas du schéma fourni ci-dessous, où on a introduit un mécanisme de conditionnement sur l'horloge CK. Pour interdire l'écriture dans la bascule, le signal C et donc le signal Z doivent rester à l'état haut. Ceci signifie que le signal Z doit rester stable pendant tout l'état bas de CK. Par ailleurs l'entrée D de la bascule doit être stable sur le front montant du signal C.

Figure 3.1 - Exemple.

3.2.1 Contraintes sur les données

En faisant des hypothèses sur les temps de propagation entre les signaux D0,D1,D2 et le signal D, donner l'expression des temps de setup et de hold des données D0,D1,D2 par rapport au front montant de l'horloge CK.

3.2.2 Contraintes sur les commandes

En faisant des hypothèses sur les temps de propagation entre I0,I1,I2 et Z, donner l'expression des temps de setup et de hold des commandes I0,I1,I2 autorisant l'écriture par rapport au front montant et au front descendant de l'horloge CK.

3.3 Placement/routage/extraction

Il s'agit à présent de générer la vue physique d'un circuit à partir d'un fichier écrit en STRATUS à l'aide des outil de placement/routage, extraction, validation vus dans les TPs précédents. Recopiez les différents fichiers du répertoire :

> ~trncomun/TP/2006/TP4/Fichiers/exemple

Vous avez :

- Un fichier exemple.py décrivant un petit circuit en STRATUS

- Un fichier exemple.pat décrivant des patterns

- Un fichier type.def qui contient la table de correspondance nom de type / type

- Un Makefile

Le fichier Makefile effectue les tâches suivantes :

- Génération du fichier vhdl structurel (.vst) du circuit avec STRATUS

- Validation cette netlist par ASIMUT.

- Génération du "layout" de ce circuit à l'aide de ocp et nero.

- Vérification du résultat (druc). ( Pour druc RDS_TECHNO_NAME est positionné à

/users/soft/techno/labo/035/extract/cmos_12.rds

- Extraction au format spice : la vue physique obtenue. L'extraction se fait avec

cougar -t

en positionnant RDS_TECHNO_NAME à

/users/soft/techno/labo/035/extract/prol035.rds

( MBK_OUT_LO à spi et MBK_SPI_MODEL au fichier type)

3.4 Etude avec eldo

D'après le schéma du circuit ci-dessus, déterminer par simulation sous ELDO (dans les conditions pire cas, c'est-à-dire VDD = 3.3 V et le fichier de paramètres de modèles .wc), les temps de propagation des 8 portes externes à la bascule SFF1. Pour toutes les entrées, en déduire, au moyen des équations obtenues en 3.2.1 et 3.2.2, les contraintes de setup-time et de hold-time.

3.5 Etude avec TAS

TAS est un analyseur temporel. Il permet d'obtenir les temps de propagation minimaux et maximaux entre les points de référence (c'est à dire les connecteurs externes et les points mémorisants) d'un circuit. TAS travaille sans stimuli, c'est pourquoi il donne des délais pire cas pour les chaînes longues.

Donner comme fichier technologie grâce à la variable d'environnement ELP_TECHNO_NAME:

/users/soft/techno/labo/035/elp/prol035.elp

Précisez le format d'entrée (.spi) dans la variable d'environnement MBK_IN_LO. Mettre en place l'environnement pour l'analyse de timing :

source /users/soft/AvtTools2003/etc/avt_env.csh

Lancer l'outil TAS grâce à la commande:

tas -t nom_de_fichier

Consulter le man de tas et essayer les differentes options pour comprendre le fonctionnement de TAS.

NB : commenter le .include dans le fichier spi pour que TAS fonctionne.

3.5.1 Chaines longues

A l'aide de TAS, et du fichier "perfmodule" général .ttx généré par TAS, donner les chaines longues entre les points de référence du circuit, et leur temps. Pour cela on utilisera XTAS qui permet d'interpreter les résultats de TAS. Disposant lui aussi d'un man, XTAS est agrémenté d'une aide en ligne. Lancer l'outil XTAS grâce à la commande:

xtas

3.5.2 Détail d'une chaine

A l'aide d'XTAS, donner le détail de la chaine la plus longue, pour chaque couple de points d'arrêt (sortie, point mémorisant).

3.6 Comparaison entre TAS et ELDO

Si on considère que les commandes I0, I1, I2 et les données D0, D1, D2 peuvent êtres confondues sous le terme plus général d'entrées, donner les temps de setup et de hold des entrées par rapport au front descendant de ck. A l'aide des résultats fournis par TAS, donner numériquement les temps de setup et de hold pour le circuit étudié. Comparer ces résultats avec ceux donnés par la simulation sous ELDO.

3.6.1 Vérification temporelle de l'AMD

Vous allez réaliser l'analyse statique temporelle de l'AMD du TP3, grâce à l'extraction que vous devez réaliser au niveau transistor, en positionnant RDS_TECHNO_NAME comme précédemment. Lancez l'outil TAS sur le fichier de l'AMD extrait au niveau transistor, grâce à la commande:

tas -t nom_de_fichier

A l'aide de TAS et du fichier "perfmodule" général .ttx généré par TAS, donner les chaînes longues entre les points de référence du circuit et leur temps (entrées, registres, sorties). Pour cela on utilisera XTAS qui permet d'interpréter les résultats de TAS. Disposant lui aussi d'un man, XTAS est agrémenté d'une aide en ligne. Lancer l'outil XTAS grâce à la commande :

xtas

3.7 Conclusion

Ce TP vous a permis de passer par la plupart des étapes nécessaires à l'analyse et la validation temporelle d'un circuit numérique. Le compte-rendu du TP doit comporter :

- Vos logins, vos noms et prénoms, et vos répertoires de travail pour ce TP (laissez libre accès à vos répertoires en lecture !).

- Une description exacte de la méthodologie employée, incluant les éventuels problèmes rencontrés.

- l'analyse des résultats concernant le transistor et l'inverseur.

- les mesures commentés des temps caractéristiques de la bascule.

- les chaînes longues du circuit mémorisant donnés par TAS, l'analyse avec ELDO, votre interprétation de la comparaison.

- La fréquence maximum d'utilisation de votre AMD avec l'explication de votre utilisation de TAS.

NE PAS JOINDRE DE LISTINGS DE FICHIERS (SAUF LES MAKEFILES).

Merci et bon courage !

Attachments (1)

- schema1.png (19.3 KB) - added by 17 years ago.

Download all attachments as: .zip