## UNIVERSITE BRETAGNE LOIRE

THÈSE / UNIVERSITÉ BRETAGNE-SUD sous le sceau de l'Université Bretagne-Loire

pour obtenir le titre de DOCTEUR DE L'UNIVERSITÉ BRETAGNE-SUD

Mention : STIC **École doctorale : SICMA**

Présentée par Maria Méndez Real

Préparée à l'unité mixte de recherche (n° 6285)

Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance

Thèse soutenue le 20 septembre 2017 devant le jury composé de :

**Nele Mentens**

Associate Professor, KU Leuven / Reviewer

Eduardo De La Torre

Associate Professor, Universidad Politécnica de Madrid (UPM) / Reviewer

Gilles Sassatelli

CNRS Research Director, Université de Montpellier / Reviewer

Lilian Bossuet

Professor, Université Jean Monnet / Examiner

Khurram Bhatti

Assistant Professor, Technology University (TU) / Examiner

Diana Goehringer

Professor, Technische Universitaet Dresden, Germany / Examiner

Vianney Lapotre

Associate Professor, Université de Bretagne-Sud (UBS) / Thesis Co-Adviser

Guy Gogniat

Professor, Université de Bretagne-Sud (UBS) / Thesis Adviser

Spatial Isolation against Logical Cache-based Side-Channel Attacks in Many-Core Architectures

#### Résumé

L'évolution technologique ainsi que l'augmentation incessante de la puissance de calcul requise par les applications font des architectures "many-core" la nouvelle tendance dans la conception des processeurs. Ces architectures sont composées d'un grand nombre de ressources de calcul (des centaines ou davantage) ce qui offre du parallélisme massif et un niveau de performance très élevé. En effet, les architectures many-core permettent d'exécuter en parallèle un grand nombre d'applications, venant d'origines diverses et de niveaux de sensibilité et de confiance différents, tout en partageant des ressources physiques telles que des ressources de calcul, de mémoire et de communication.

Cependant, ce partage de ressources introduit également des vulnérabilités importantes en termes de sécurité. En particulier, les applications sensibles partageant des mémoires cache avec d'autres applications, potentiellement malveillantes, sont vulnérables à des attaques logiques de type canaux cachés basées sur le cache. Ces attaques, permettent à des applications non privilégiées d'accéder à des informations secrètes sensibles appartenant à d'autres applications et cela malgré des méthodes de partitionnement existantes telles que la protection de la mémoire et la virtualisation.

Alors que d'importants efforts ont été faits afin de développer des contremesures à ces attaques sur des architectures multicoeurs, ces solutions n'ont pas été originellement conçues pour des architectures many-core récemment apparues et nécessitent d'être évaluées et/ou revisitées afin d'être applicables et efficaces pour ces nouvelles technologies.

Dans ce travail de thèse, nous proposons d'étendre les services du système d'exploitation avec des mécanismes de déploiement d'applications et d'allocation de ressources afin de protéger les applications s'exécutant sur des architectures many-core contre les attaques logiques basées sur le cache. Plusieurs stratégies de déploiement sont proposées et comparées à travers différents indicateurs de performance. Ces contributions ont été implémentées et évaluées par prototypage virtuel basé sur SystemC et sur la technologie "Open Virtual Platforms" (OVP).

#### Abstract

The technological evolution and the increasing application performance demand have made of many-core architectures the new trend in processor design. These architectures are composed of a large number of processing resources (hundreds or more) providing massive parallelism and high performance. Many-core architectures allow indeed a wide number of applications coming from different sources, with a different level of sensitivity and trust, to be executed in parallel, sharing physical resources such as computation, memory and communication infrastructure.

However, this resource sharing introduces important security vulnerabilities. In particular, sensitive applications sharing cache memory with potentially malicious applications are vulnerable to logical cache-based side-channel attacks. These attacks allow an unprivileged application to access sensitive information manipulated by other applications despite partitioning methods such as memory protection and virtualization.

While a lot of efforts on countering these attacks on multi-core architectures have been done, these have not been designed for recently emerged many-core architectures and require to be evaluated, and/or revisited in order to be practical for these new technologies.

In this thesis work, we propose to enhance the operating system services with security-aware application deployment and resource allocation mechanisms in order to protect sensitive applications against cached-based attacks. Different application deployment strategies allowing spatial isolation are proposed and compared in terms of several performance indicators. Our proposal is evaluated through virtual prototyping based on SystemC and Open Virtual Platforms (OVP) technology.

### Remerciements

Ce manuscrit présente des travaux que j'ai effectués dans le cadre de ma thèse durant trois ans au laboratoire Lab-STICC. Je tiens à remercier les personnes de ce laboratoire qui ont permis à ce travail d'être réalisé dans des bonnes conditions et dans une bonne ambiance. Aussi, je remercie les personnes du laboratoire IETR qui m'ont permis de finaliser la préparation de ma soutenance de thèse dans des bonnes conditions.

Je remercie tous les membres du jury, mes rapporteurs Nele Mentens, Eduardo De La Torre et Gilles Sassatelli, mes examinateurs Diana Goehringer et Khurram Bhatti ainsi que Lilian Bossuet, examinateur et président de mon jury de thèse. Je les remercie d'avoir participé à la soutenance de ma thèse, de s'y être investi de manière aussi enthousiaste et d'avoir montré leur intérêt dans mes travaux de thèse. Je les remercie également pour leurs commentaires, leurs questions et leurs conseils.

Je remercie chaleureusement mon directeur et encadrant de thèse Guy Gogniat et mon encadrant Vianney Lapôtre. Merci de toujours avoir réussi à trouver du temps pour moi malgré vos emplois du temps serrés, de nos discussions, de votre encouragement et conseils, ainsi que et de la confiance dont vous m'avez toujours témoignée. Travailler avec vous a été un vrai plaisir et j'espère que nous aurons l'occasion de collaborer ensemble à nouveau.

Je remercie également tous les partenaires du projet TSUNAMY ainsi que l'équipe MCA de l'Université de la Ruhr à Bochum des collaborations que nous avons pu mener lors de ma thèse.

Aussi, je remercie mes collègues et mes amis au sein du laboratoire dont la liste est longue. Merci à tous de votre soutien, de votre aide et de votre bonne humeur.

Finalement je remercie ma famille proche et mon mari et meilleur ami Baptiste Goupille-Lescar de m'avoir toujours rassurée et encouragée.

## Contents

| Li            | List of Figures v |                                                           |    |  |  |

|---------------|-------------------|-----------------------------------------------------------|----|--|--|

| $\mathbf{Li}$ | st of             | Tables                                                    | ix |  |  |

| $\mathbf{Li}$ | st of             | Algorithms                                                | xi |  |  |

| 1             | Inti              | roduction and context                                     | 1  |  |  |

|               | 1.1               | Introduction                                              | 1  |  |  |

|               |                   | 1.1.1 TSUNAMY project                                     | 3  |  |  |

|               | 1.2               | Context                                                   | 5  |  |  |

|               |                   | 1.2.1 Considered system                                   | 6  |  |  |

|               |                   | 1.2.2 Attacks characterization and threat model           | 8  |  |  |

|               |                   | 1.2.3 Threat model considered in this thesis work         | 11 |  |  |

|               |                   | 1.2.4 Introduction to logical cache-based attacks         | 12 |  |  |

|               | 1.3               | Contributions                                             | 18 |  |  |

|               | 1.4               | Organization of the manuscript                            | 20 |  |  |

| 2             | Sta               | te of the art                                             | 23 |  |  |

|               | 2.1               | Software and hardware cache-based attacks countermeasures | 23 |  |  |

|               |                   | 2.1.1 Software cache-based attacks countermeasures        | 24 |  |  |

|               |                   | 2.1.2 Hardware cache-based attacks countermeasures        | 27 |  |  |

|               | 2.2               | Logical and physical isolation                            | 33 |  |  |

|               | 2.3               | Discussion                                                | 40 |  |  |

| 3             | Spa               | tial isolation                                            | 43 |  |  |

|               | 3.1               | Spatial isolation                                         | 43 |  |  |

ii CONTENTS

| 3.2   | Different deployment strategies for spatial isolation                      |

|-------|----------------------------------------------------------------------------|

|       | 3.2.1 Static size secure zone approach                                     |

|       | 3.2.2 Fully dynamic size secure zone approach                              |

|       | 3.2.3 Trade-off strategies combining both, static and dynamic approaches 5 |

| 3.3   | Summary of the proposed deployment strategies                              |

| 3.4   | Extension of the kernel services for spatial isolation implementation      |

|       | 3.4.1 Threat model and assumptions                                         |

|       | 3.4.2 ALMOS kernel services and integration of spatial isolation 6         |

| 3.5   | Summary of the extensions of the kernel services                           |

| 3.6   | Conclusion                                                                 |

| 4 Ex  | tension and exploration of MPSoCSim 7                                      |

| 4.1   | Motivation                                                                 |

| 4.2   | MPSoCSim                                                                   |

|       | 4.2.1 Imperas/Open Virtual Platforms (OVP) technology                      |

|       | 4.2.2 Network-on-Chip (NoC) simulator                                      |

| 4.3   | Validation                                                                 |

|       | 4.3.1 Hardware implementation                                              |

|       | 4.3.2 Experimental protocol                                                |

|       | 4.3.3 Evaluation results                                                   |

| 4.4   | MPSoCSim extension                                                         |

|       | 4.4.1 Clustering the architecture                                          |

|       | 4.4.2 Dynamic execution capabilities                                       |

| 4.5   | Exploration with the extended MPSoCSim version                             |

|       | 4.5.1 Exploration protocol                                                 |

|       | 4.5.2 MPSoCSim available results                                           |

|       | 4.5.3 Exploration results                                                  |

| 4.6   | Conclusion                                                                 |

| 5 Spa | atial isolation evaluation through virtual prototyping 9                   |

| 5.1   | Experimental protocol                                                      |

| 5.2   | Cache attacks vulnerability case study                                     |

| 5.3   | Deployment strategies comparison results                                   |

|       | 5.3.1 Considered deployment and execution scenarios                        |

|       | 5.3.2 Results organization                                                 |

| CONTENTS | iii |

|----------|-----|

|          |     |

| 5.4                                      | 5.3.3<br>5.3.4<br>5.3.5<br>4 Concl | Comparison according to each performance indicator | . 108<br>. 110 |

|------------------------------------------|------------------------------------|----------------------------------------------------|----------------|

| 6 Co                                     | onclusio                           | on and future work                                 | 117            |

| 6.1                                      | Sumn                               | nary                                               | . 117          |

| 6.2                                      | 2 Spatia                           | al isolation discussion                            | . 118          |

|                                          | 6.2.1                              | Back to the state-of-the-art                       | . 118          |

|                                          | 6.2.2                              | Further attacks and spatial isolation capabilities | . 120          |

| 6.3                                      | B Possil                           | ole improvements and leads for future work         | . 121          |

| 6.4                                      | 4 Concl                            | usion                                              | . 128          |

| Gloss                                    | sary                               |                                                    | 129            |

| List of publications and presentations 1 |                                    | 131                                                |                |

| Bibliography 135                         |                                    | 135                                                |                |

iv CONTENTS

# List of Figures

| Moore's law                                                                                                                                      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSUNAMY context                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Overview of the considered system                                                                                                                | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Principle of PRIME+PROBE [29] attack                                                                                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Cache partitions using page coloring                                                                                                             | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Attack on NoC communication                                                                                                                      | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

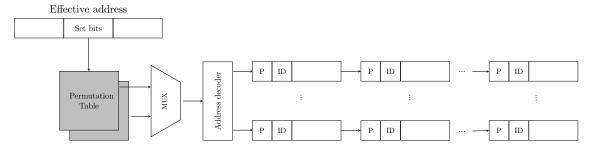

| A logical view of the RPcache permutation [69]                                                                                                   | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

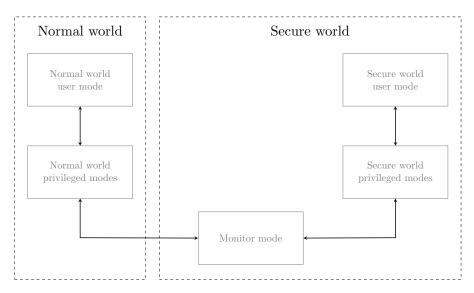

| Cache access handling in RPcache [69]                                                                                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

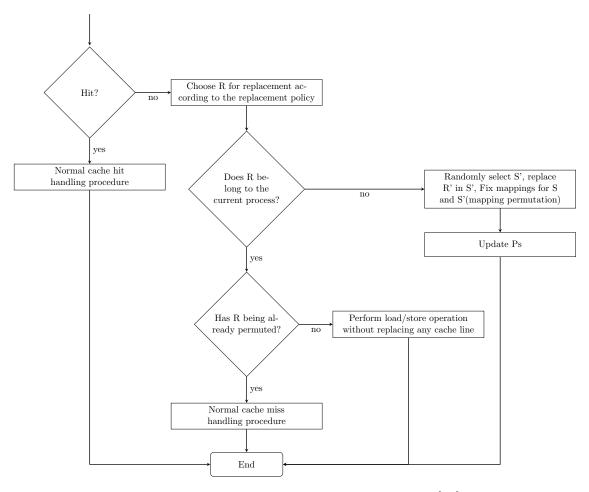

| Memory Management Unit (MMU)                                                                                                                     | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

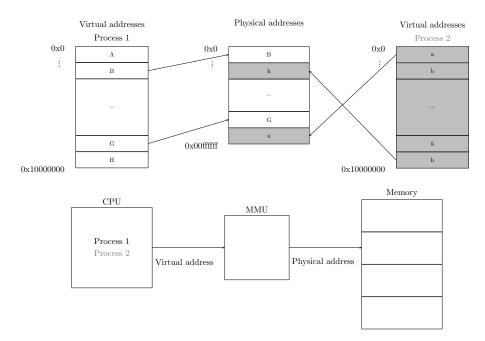

| Modes in ARM core with TrustZone extensions [81]                                                                                                 | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

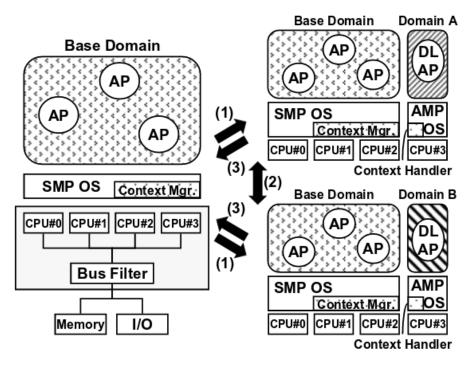

| Dynamic security domains [83]                                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Extension of SCC for resource isolation [84]                                                                                                     | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

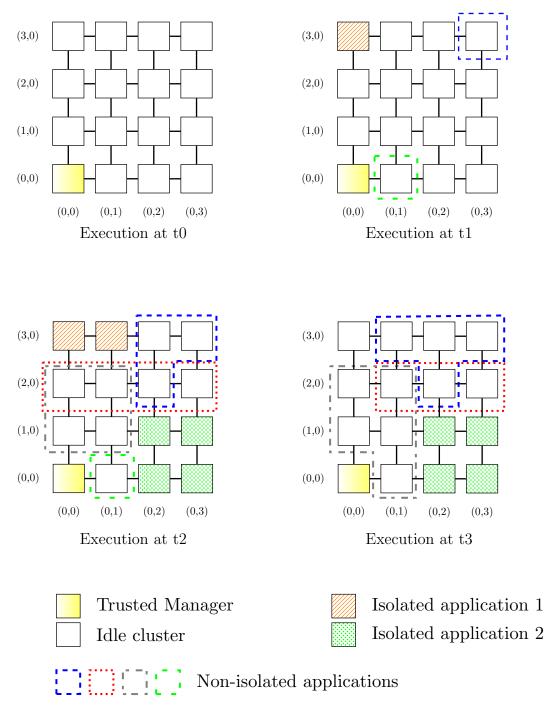

| Principle of spatial isolation                                                                                                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

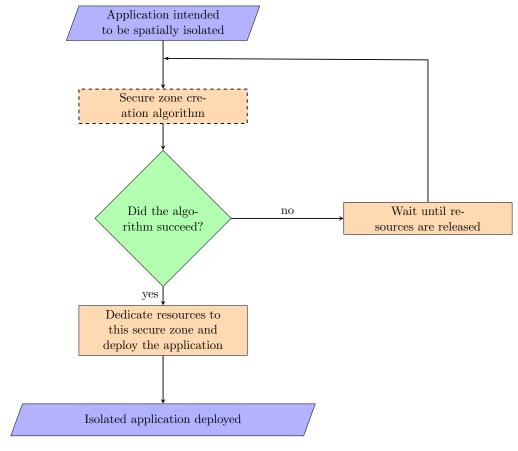

| Creating a Secure Zone                                                                                                                           | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Overview of the creation of a static size secure zone flow                                                                                       | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Exploration of clusters in secure zone creation algorithms                                                                                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

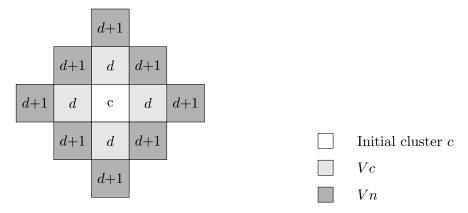

| Overview of the dynamic approach with a guaranteed non-optimized secure zone size approach                                                       | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

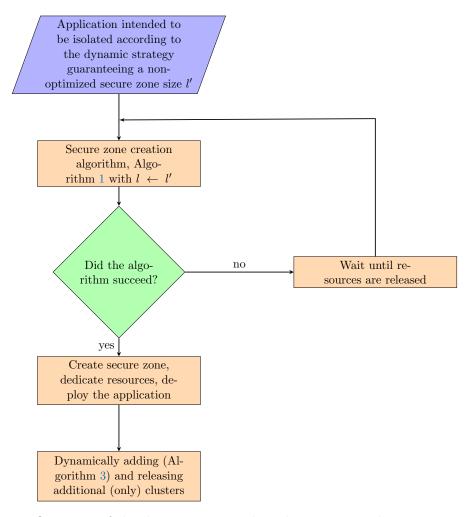

| Overview of the resource reservation approach                                                                                                    | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Overview of the kernel monitoring structure                                                                                                      | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

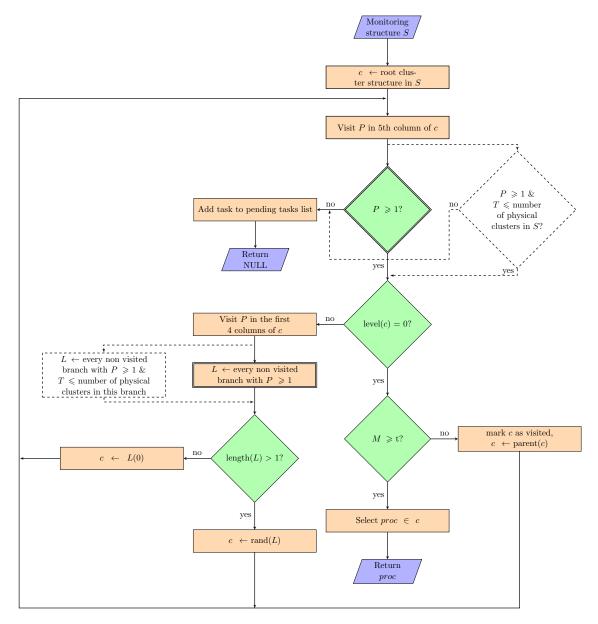

| Overview of original kernel application mapping algorithm and its extension in dashed lines (double line nodes are replaced by dashed line ones) | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

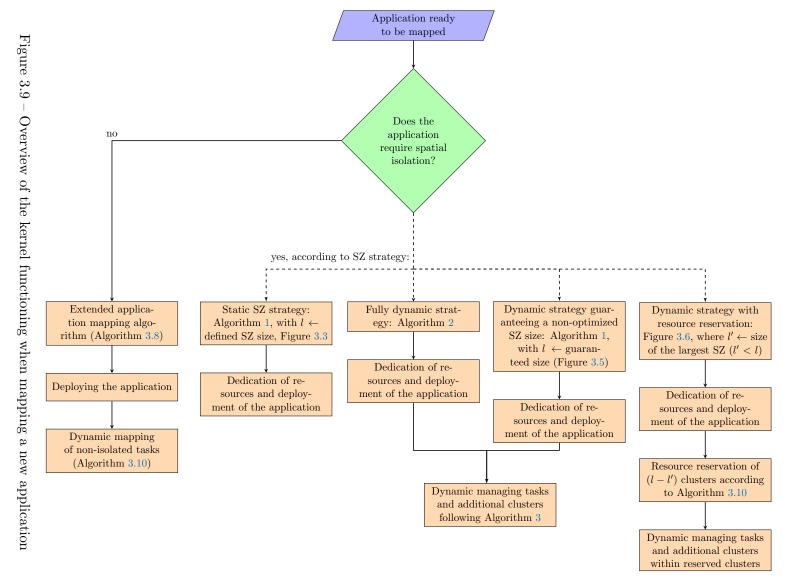

|                                                                                                                                                  | TSUNAMY context Overview of the considered system Principle of PRIME+PROBE [29] attack  Cache partitions using page coloring Attack on NoC communication A logical view of the RPcache permutation [69] Cache access handling in RPcache [69] Memory Management Unit (MMU) Modes in ARM core with TrustZone extensions [81] Dynamic security domains [83] Extension of SCC for resource isolation [84]  Principle of spatial isolation Creating a Secure Zone Overview of the creation of a static size secure zone flow Exploration of clusters in secure zone creation algorithms Overview of the dynamic approach with a guaranteed non-optimized secure zone size approach Overview of the kernel monitoring structure |

vi LIST OF FIGURES

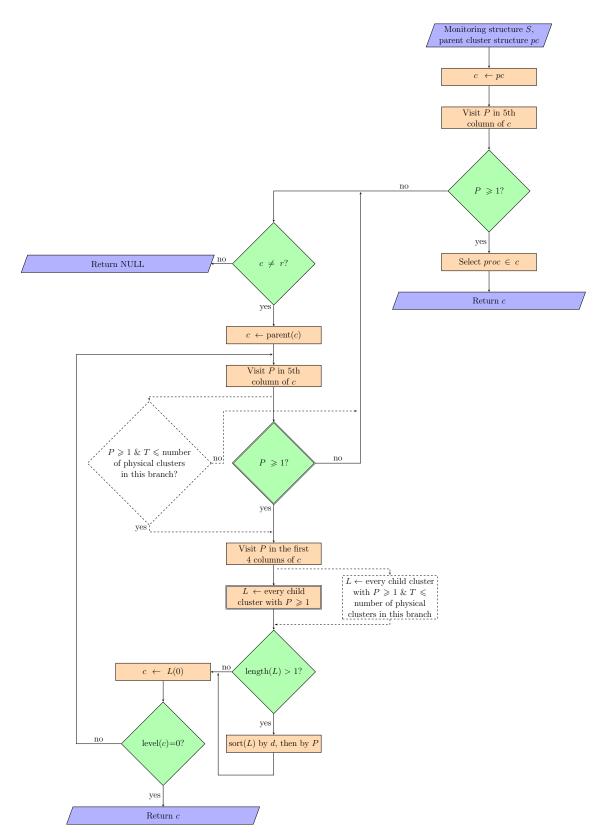

| 3.10 | Overview of original kernel task mapping algorithm and its extension in dashed lines (double line nodes are replaced by dashed line ones)                                                                                                      | 67  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

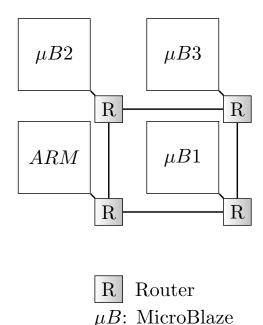

| 4.1  | 2D-Mesh NoC for MPSoCSim validation                                                                                                                                                                                                            | 78  |

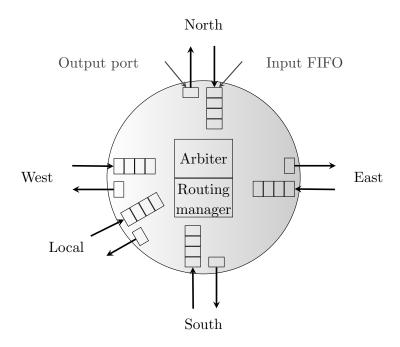

| 4.2  | MPSocSim router structure                                                                                                                                                                                                                      | 79  |

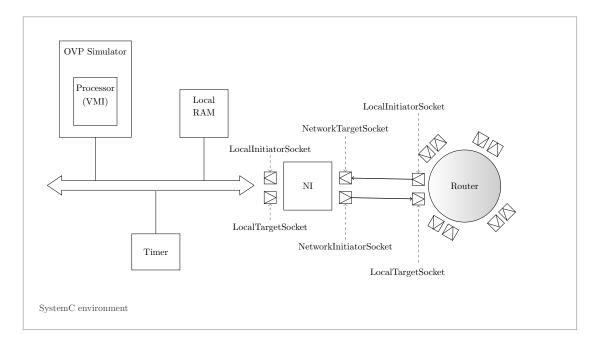

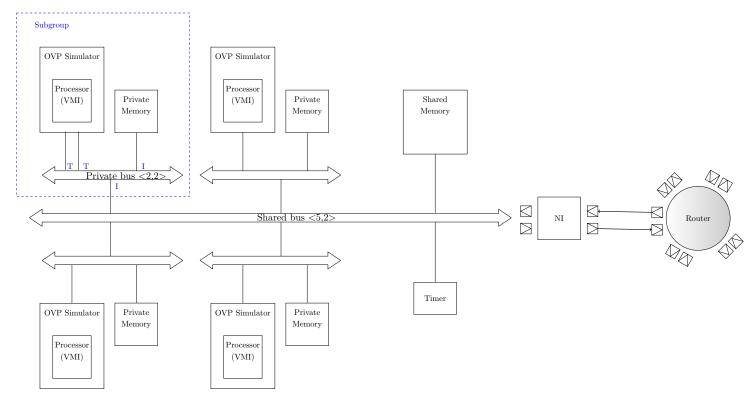

| 4.3  | MPSocSim simulator overview                                                                                                                                                                                                                    | 80  |

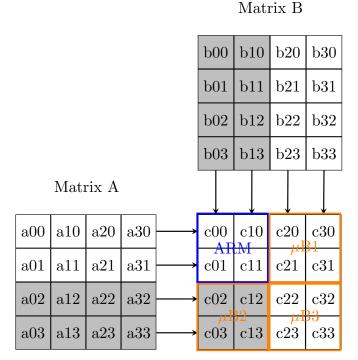

| 4.4  | Tiled matrix multiplication [90]                                                                                                                                                                                                               | 82  |

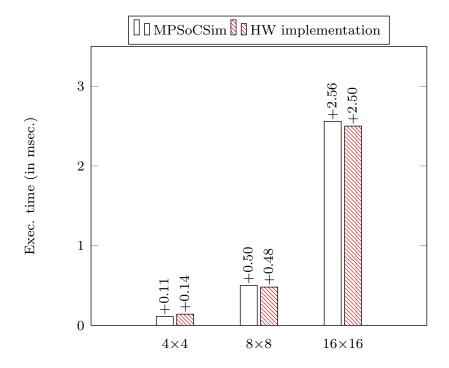

| 4.5  | Comparison between MPSoCSim and the hardware implementation $[90]$                                                                                                                                                                             | 83  |

| 4.6  | Overview of the extended MPSoCSim                                                                                                                                                                                                              | 85  |

| 4.7  | Considered platform instantiation                                                                                                                                                                                                              | 86  |

| 4.8  | OVP ARM processor instantiation parameters                                                                                                                                                                                                     | 87  |

| 4.9  | OVP MicroBlaze processor instantiation parameters                                                                                                                                                                                              | 87  |

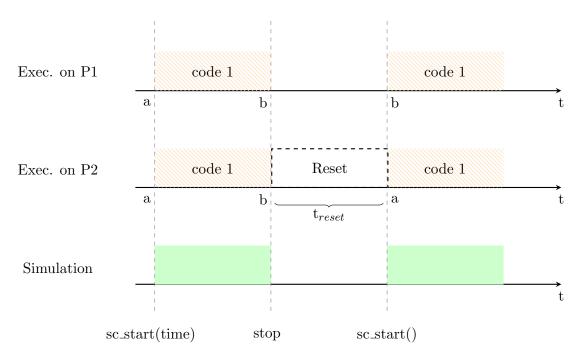

| 4.10 | First possible case of dynamic execution simulation                                                                                                                                                                                            | 88  |

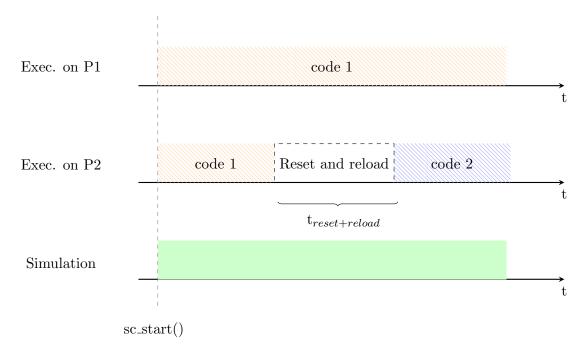

| 4.11 | Second possible case of dynamic execution simulation                                                                                                                                                                                           | 89  |

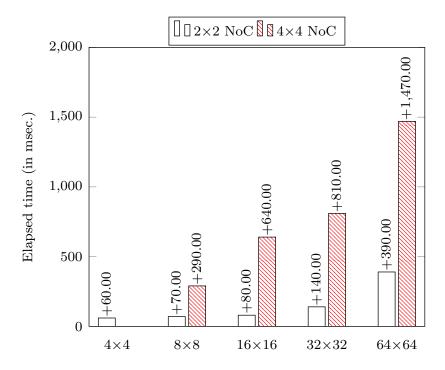

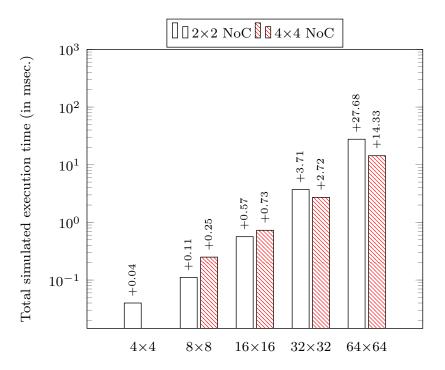

| 4.12 | <b>Elapsed time</b> (in msec.) for different sizes of matrix multiplications on $2\times2$ and $4\times4$ NoC clustered architectures (12 MicroBlazes and 1 ARM, and 60 MicroBlazes and 1 ARM respectively)                                    | 91  |

| 4.13 | <b>Total simulated execution time</b> (in msec.) for different sizes of matrix multiplications on a 2×2 and 4×4 NoC clustered architectures (12 MicroBlazes and 1 ARM, and 60 MicroBlazes and 1 ARM respectively)                              | 92  |

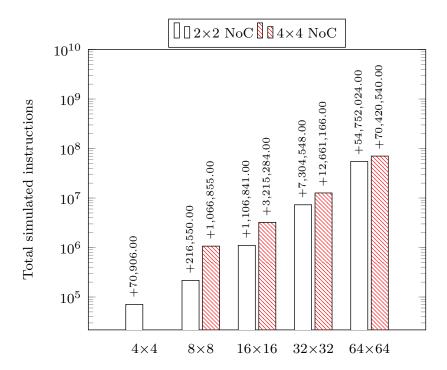

| 4.14 | <b>Total simulated instructions</b> for the execution of different sizes of matrix multiplications on 2×2 and 4×4 NoC clustered architectures (12 MicroBlazes and 1 ARM, and 60 MicroBlazes and 1 ARM respectively)                            | 93  |

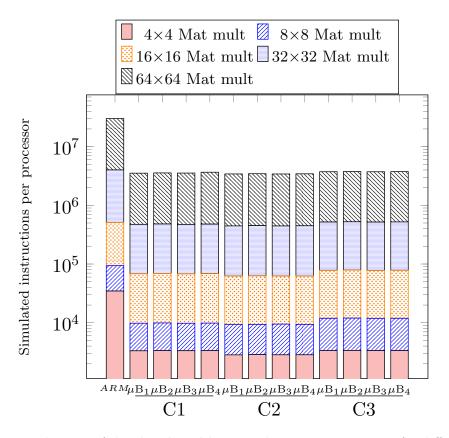

| 4.15 | Evaluation of the <b>simulated instructions per processor</b> for different sizes of matrix multiplications on a $2\times2$ architecture (12 MicroBlazes and 1 ARM)                                                                            | 94  |

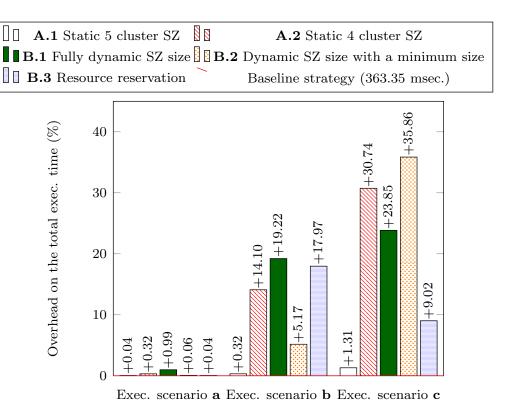

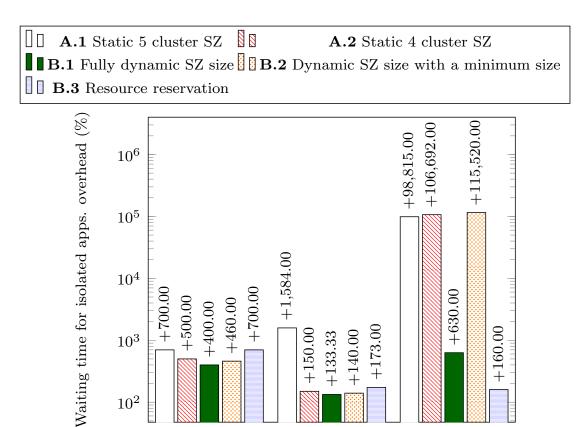

| 5.1  | Total execution time overhead (in percentage) compared to the Baseline strategy for each couple of secure zone deployment strategy and execution scenario                                                                                      | 105 |

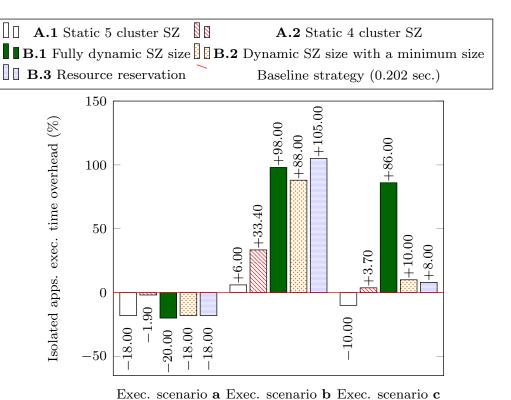

| 5.2  | Overhead on the average <i>execution time of isolated applications</i> , in terms of percentage of the average application execution time in the Baseline strategy for each couple of secure zone deployment strategy and execution scenario . | 107 |

LIST OF FIGURES vii

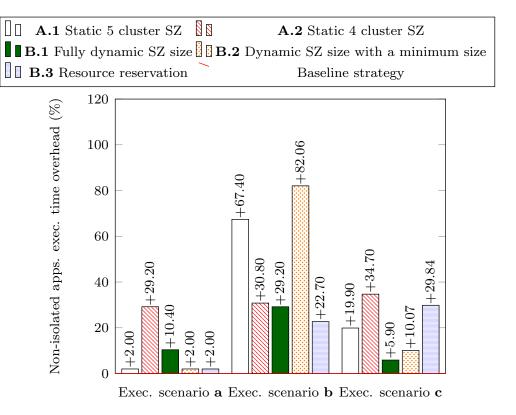

| 5.3 | Overhead on the average execution time of non-isolated applications, in               |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | terms of percentage of the average application execution time in the Baseline         |     |

|     | strategy for each couple of secure zone deployment strategy and execution             |     |

|     | scenario                                                                              | 108 |

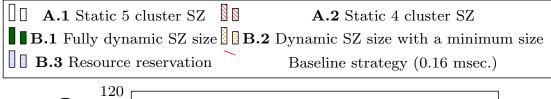

| 5.4 | Time spent on the trusted manager kernel services impacted by the secure-             |     |

|     | enable mechanisms in terms of percentage compared to the Baseline strategy            |     |

|     | for each couple of secure zone deployment strategy and execution scenario .           | 109 |

| 5.5 | Overhead on the average waiting time before the deployment of isolated                |     |

|     | applications, in terms of percentage compared to the Baseline strategy, for           |     |

|     | each couple of secure zone deployment strategy and execution scenario                 | 110 |

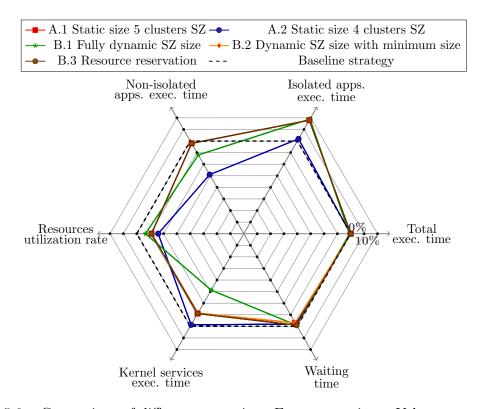

| 5.6 | Comparison of different strategies - Exec. scenario a. Values are presented           |     |

|     | in terms of induced overhead in percentage with respect of the baseline value.        |     |

|     | Arranged scale: the closest to the chart, the better. Scale: 1 division: 10%          | 112 |

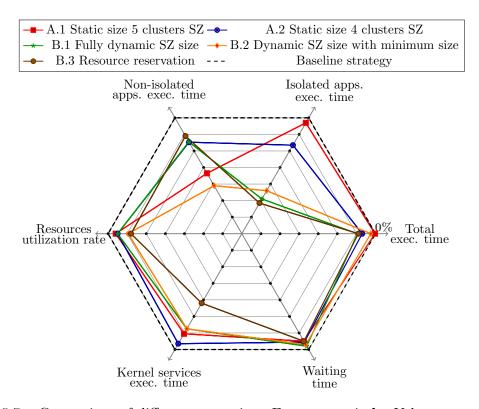

| 5.7 | Comparison of different strategies - Exec. scenario b. Values are presented           |     |

|     | in terms of induced overhead in percentage with respect of the baseline value.        |     |

|     | Arranged scale: the closest to the chart, the better. Scale: 1 division: 20%          | 113 |

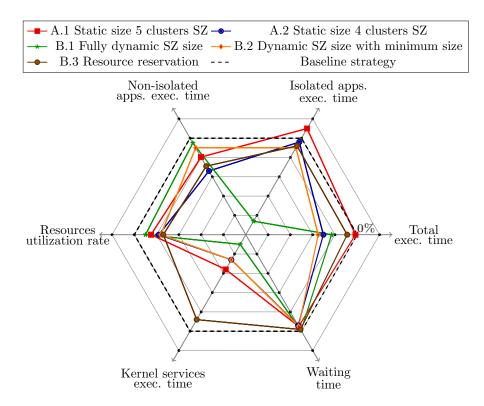

| 5.8 | Comparison of different strategies - Exec. scenario ${f c}$ . Values are presented in |     |

|     | terms of induced overhead in percentage with respect of the baseline value.           |     |

|     | <b>Arranged scale</b> : the closest to the chart, the better. Scale: 1 division: 20%  | 114 |

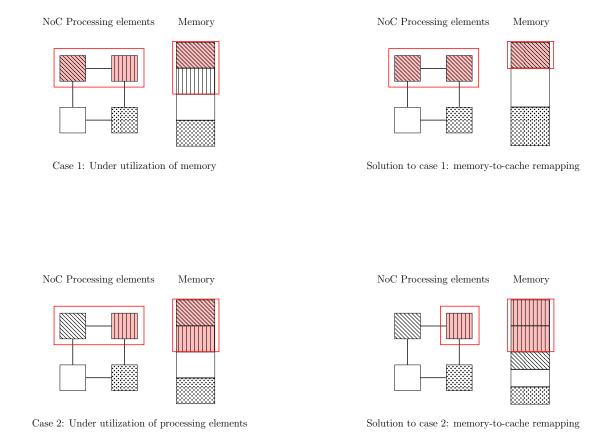

| 6.1 | Dynamic memory-to-cache mapping to reduce under-utilization or resources              | 126 |

## List of Tables

| 1.1        | Categories of logical attacks according to the threaten security property                                                                                                                                                                                                                                                                                                                  | 11  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1        | Comparison of state-of-the-art countermeasures                                                                                                                                                                                                                                                                                                                                             | 41  |

| 3.1<br>3.2 | Summary of the different proposed strategies                                                                                                                                                                                                                                                                                                                                               |     |

| 4.1<br>4.2 | Overview of the existing simulators supporting NoC infrastructure System parameters used for evaluation in MPSoCSim                                                                                                                                                                                                                                                                        |     |

| 5.1        | Cache-based attacks vulnerability in the Baseline strategy where the average resources utilization rate is $77\%$                                                                                                                                                                                                                                                                          | 101 |

| 5.2        | Resources utilization rate within secure zone(s) as well as in total (referred to as Secure zone and Total in the table) for each couple of secure zone deployment strategy and execution scenario. For each SZ and Total columns, the best and worst resources utilization rates are highlighted in light gray and dark gray respectively. The resources utilization rate in the Baseline |     |

|            | strategy is 77%                                                                                                                                                                                                                                                                                                                                                                            | 111 |

| 5.3        | Selecting the deployment strategy summary                                                                                                                                                                                                                                                                                                                                                  | 115 |

x LIST OF TABLES

# List of Algorithms

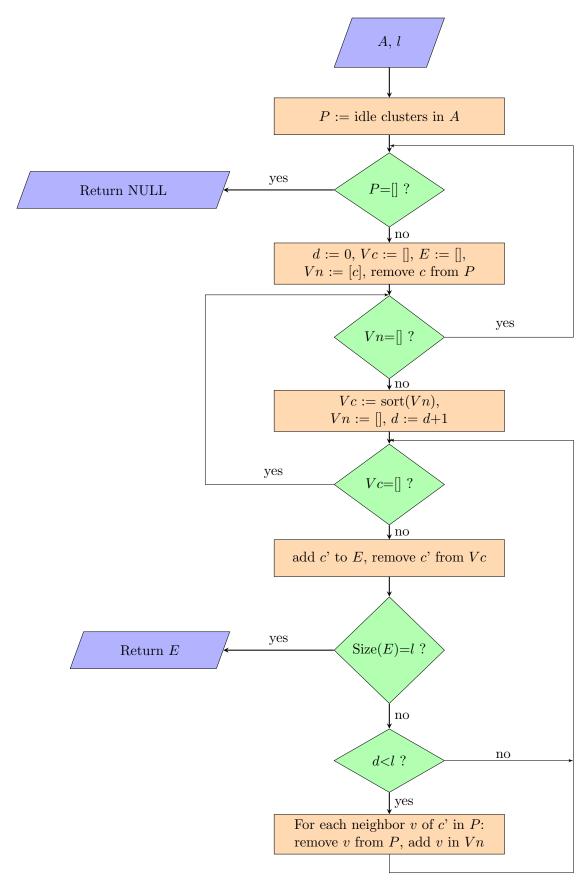

| 1 | Creating a fixed secure zone         | 50 |

|---|--------------------------------------|----|

| 2 | Creating a fully dynamic secure zone | 52 |

| 3 | Extending a dynamic size Secure Zone | 53 |

### Chapter 1

### Introduction and context

#### Chapter contents

| 1.1 | Introduction                                    |

|-----|-------------------------------------------------|

| 1.  | 1.1 TSUNAMY project                             |

| 1.2 | Context                                         |

| 1.  | 2.1 Considered system                           |

| 1.  | 2.2 Attacks characterization and threat model   |

| 1.  | 2.3 Threat model considered in this thesis work |

| 1.  | 2.4 Introduction to logical cache-based attacks |

| 1.3 | Contributions                                   |

| 1.4 | Organization of the manuscript 20               |

In this chapter, a general introduction of this thesis work including the TSUNAMY project presentation, is first given. After, the system and the associated threat model are presented. Contributions are then presented and the organization of this manuscript is explained.

#### 1.1 Introduction

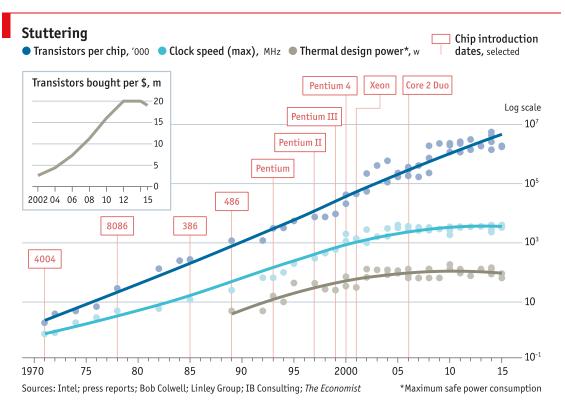

The technological evolution has made possible the constant increase of transistor density. This evolution has been quantified by Gordon Moore, Intel co-founder, in 1965, by the empirical so called Moore's law. This law states that the number of transistors per square inch on integrated circuits will double every year [1]. Indeed, since that time, the number of transistors has doubled every 18 months approximately (Figure 1.1).

Figure 1.1 – Moore's law

Reducing the technology size makes possible to double the number of transistors but also to reduce the distance between them on the circuit. Consequently, circuits are more complex and the processing frequency is increased. However, the frequency improvement penalizes power consumption, which in turn generates heat, and increases leakage current. This trend introduces important issues; more advanced cooling is required, Thermal Design Power (TDP) constrains the amount of circuitry of the chip that can be powered-on at the nominal operating voltage (dark silicon), the decreasing distance between transistors entails important capacitance effects (cross talk capacitance), reducing the reliability of the system, and the circuit longevity is shortened.

A more cost-efficient alternative is to replicate multiple processing cores on a single die. These work in parallel, share memory and are connected via an on-chip bus. Following this trend, many-core architectures have been more recently emerged. These architectures, in contrast to multi-core, are composed of hundreds (or more) simpler and very efficient processing cores. Many-core architectures include private and shared memory, can encom-

pass heterogeneous processing resources offering great flexibility. Finally, these improve the performance of parallel computing applications as they offer a wide number of computing resources and optimize the communication between cores. For this purpose, applications running in parallel share physical resources for computation, data storage and communication. Existing commercial high-performance parallel computing platforms based on many-core architectures include [2][3][4][5][6].

These architectures are likely to be used, potentially remotely, in systems shared by mutually untrusted parties. For instance, in public and private clouds, where Virtual Machines (VMs) are supplied to untrusted parties on remote platforms, each executing applications coming from different sources, with a different level of sensitivity and trust. These are particularly suitable in a High Performance Computing (HPC) environment.

Given the potential wide use of many-core architectures in security-critical systems and the massive resource sharing enabled by these technologies, it is clear that the issue of security when accessing and handling data on these architectures as well as the protection of personal data for each user are critical.

Many-core architectures must guarantee the integrity and confidentiality of applications as well as the protection of user's personal data in order to ensure their adoption.

While security has been widely addressed in multi-core systems, mainly through logical isolation (see Chapter 2), existing solutions must be evaluated and/or revisited in order to provide a reliable solution suitable for many-core systems.

We particularly focus on software (also called logical) Side-Channel Attacks (SCAs). These attacks allow an unprivileged process to access sensitive information about other processes despite partitioning methods such as memory protection, sandboxing and virtualization.

#### 1.1.1 TSUNAMY project

The national TSUNAMY project (2013-2017) [7] supported by the Agence Nationale de la Recherche (ANR) addresses the problem of secure handling of personal data and privacy in many-core architectures.

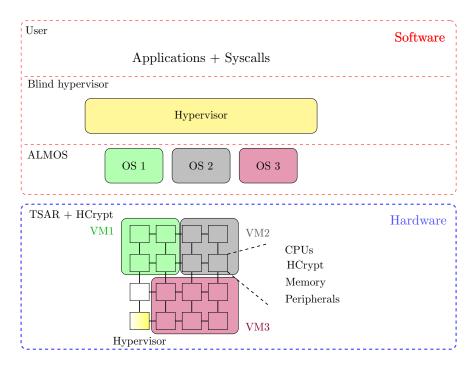

The considered system as well as the positioning of the proposed contributions are illustrated in Figure 1.2. In this figure, the hardware and software layers of the system are presented. The hypervisor is responsible for allocating VMs and ensuring the non interference between them. A VM is deployed on a certain number of physical resources on the hardware platform. This latter is heterogeneous and encompasses generic processing ele-

Figure 1.2 – TSUNAMY context

ments for generic computation, as well as dedicated resources for cryptographic algorithms. One VM is allocated to each user. Each VM is considered to run an entire Operating System (OS). Consequently, several OS might run in parallel on different VMs on the hardware platform.

The aim of the TSUNAMY project is then to propose mixed hardware and software solutions allowing to execute numerous independent applications, while providing an isolated execution environment as a response to confidentiality and integrity issues. For this purpose, several partners are involved:

- CEA LIST Commissariat à l'Energie Atomique et aux Energies Alternatives,

- LIP6 Laboratoire d'Informatique de Paris 6, CNRS UMR 7606,

- LabHC Laboratoire Hubert Curien, CNRS UMR 5516 and

- Lab-STICC Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance, CNRS UMR 6285.

Several significant contributions are proposed:

• joint development of software layers (driver, API ...) and hardware mechanisms to provide a chain of trust,

- development of a heterogeneous architecture encompassing processing elements to run both, algorithms for processing information and cryptographic algorithms with a strong level of coupling for performance reasons but while ensuring no leakage of information (TSAR [8] + HCrypt [9] in Figure 1.2),

- development of a software layer with limited rights on the system execution ensuring the physically isolated deployment and execution of VMs (blind hypervisor [10] in Figure 1.2),

- development of mechanisms for logical and physical isolation in order to ensure isolated execution of concurrent applications within each Virtual Machine (VM) (AL-MOS in Figure 1.2) and

- development of strategies for dynamically distributing applications on a many-core architecture (ALMOS in Figure 1.2).

The implementation and evaluation of the contributions in the frame of the TSUNAMY project, rely on the TSAR many-core architecture [8] and ALMOS OS [11] (both presented in Chapter 1, Section 1.2.1). The TSAR architecture is enhanced with HCrypt cryptoprocessor [12]. Finally, a blind hypervisor [13] is integrated in order to manage the allocation and management of VMs.

The work of this thesis in the frame of the TSUNAMY project focuses on the secure execution of applications within a VM on the TSAR architecture. The aim is to develop mechanisms and study different dynamic application deployment strategies for the logical and physical isolated execution of concurrent applications.

#### 1.2 Context

In this subsection, the system and the corresponding threat model considered in this thesis work are presented. Finally, logical cache-based side-channel attacks, addressed in this work, are introduced.

#### 1.2.1 Considered system

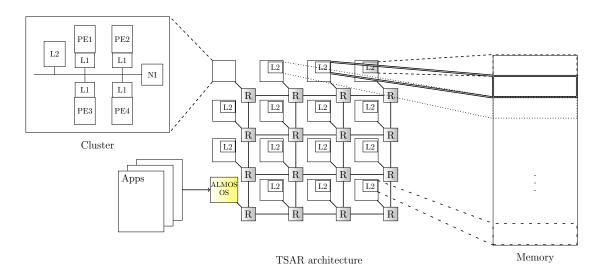

#### The TSAR architecture

Many-core architectures are composed of a large number of simple independent processing cores (from tens to hundreds or more). Many-core architectures are divided into clusters composed of processing or memory elements. Clusters can be more complex encompassing several processing and memory elements such as local memory and a cache hierarchy. Within each complex cluster, several cores are connected through a local interconnect and can access some private resources (e.g., private memory, memory caches) as well as some local resources shared among cores within the same cluster as local memory, caches and peripherals among others. Clusters are usually connected through a NoC [14].

Some examples of many-core architectures are the academic TSAR architecture [8], and the industrial Kalray's Massively Parallel Processor Array (MPPA) [2], Mellanox' TILE-Gx36 [3] and TILE-Gx72 [4] processors, Adapteva's Epiphany co-processor [5] and Intel's Xeon Phi [6].

The baseline many-core architecture used in the TSUNAMY project is the TSAR architecture [8], which is a homogeneous many-core architecture with hardware cache coherence and virtual memory support, but no particular mechanism for addressing security issues.

TSAR is a cache-coherent, shared-memory many-core that was jointly designed by BULL, LIP6 and CEA-LETI in the framework of the European CATRENE SHARP project.

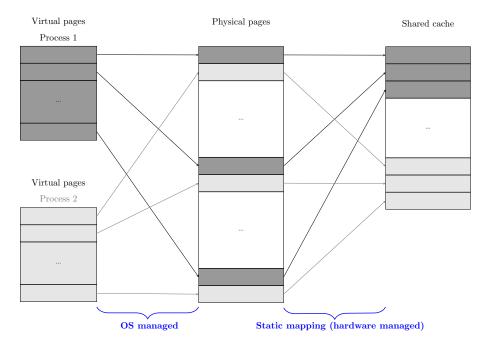

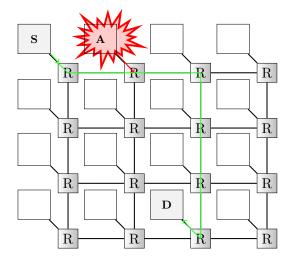

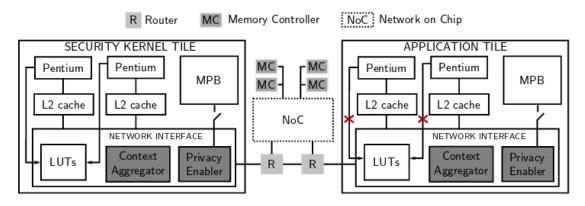

TSAR, illustrated in Figure 1.3, is composed of clusters interconnected with a 2D-Mesh NoC. Clusters encompass up to 4 Processing Elements (PEs). Each one has a private level 1 data and level 1 instruction cache (L1). Every L1 has its own Memory Management Unit (MMU) with a separated (instructions and data) Translation Look-aside Buffer (TLB). Additionally, each cluster contains a network interface, some internal peripherals and a level 2 cache (L2) memory bank accessible by all the PEs in the system. In the TSAR version considered in this thesis work, L2 is the Last Level Cache (LLC).

One of the particularities of TSAR is its memory hierarchy. In fact, the memory is logically shared but physically distributed. Every memory location is accessible by every Processing Element (PE) in the system, but the address space (1 TeraByte) is statically partitioned into a fixed number of segments (equal to the number of clusters in the architecture). Each segment is statically mapped on a L2 memory bank (see Figure 1.3). Thus, each cluster L2 memory bank is in charge of one memory segment. Consequently, TSAR

Figure 1.3 – Overview of the considered system

is a Non-Uniform Memory Access (NUMA) architecture. This implies that the memory latency is not uniform but depends on the distance between the PE cluster requesting the memory access and the target memory location cluster.

This memory hierarchy particularity of TSAR, that was initially designed in order to allow a locality aware deployment, is suitable as well for the implementation of the security mechanisms proposed in this work.

Regarding cache coherence, since L1 caches are private and L2 caches are shared, TSAR implements a hardware cache-coherence protocol called Distributed Hybrid Cache Coherence Protocol (DHCCP) [8]. L1 cache implements a write-through policy while the L2 cache implements a write-back policy. Finally, the TSAR architecture is prototyped with a Cycle-Accurate-Bit-Accurate (CABA) SystemC-based simulator [15]. This simulator is able to do accurate full-system simulation at the price of significant simulation time (2000 simulated cycles per second [16]).

The considered system is illustrated in Figure 1.3. It is composed of a TSAR-like clustered NoC-based many-core architecture controlled by ALMOS OS.

#### The ALMOS OS

ALMOS stands for Advanced Locality Management Operating System [11]. It is an academic UNIX-like OS designed for enforcing the locality of memory accesses made by

parallel tasks applications in order to minimize communication latency and power consumption. The principal OS services required for the fine management of hardware resources are described in Chapter 3, Section 3.4.2.

The TSAR architecture and ALMOS OS are used as the baseline system of this thesis work. The main objective being the protection of the system, in next subsection, the considered attacks are introduced and the associated threat model is presented.

#### 1.2.2 Attacks characterization and threat model

In this subsection, the main guarantees to provide when securing a system are first introduced. After, possible threats and attacks are presented. Then, the Trusting Computed Base (TCB) as well as the threat model associated to the many-core system, considered in this work, are presented.

Secure and reliable systems guarantee the following properties:

- Availability: the availability property guarantees the reliable access to information and to available resources by authorized actors.

- Confidentiality: confidentiality, or privacy, ensures that sensitive information is never reached by unauthorized actors by guaranteeing the respect of a set of rules and access rights.

- Integrity: integrity is the property, that the information is never accessed by an authorized actor. This property guarantees the information is not modified or erased by an unauthorized actor.

However, these properties can be attacked through either, physical and logical attacks. Both categories are presented below.

#### Categories of attacks

Two different types of attacks are distinguished according to the required access on the system:

Hardware or physical attacks: these refer to attacks that require direct access to the

physical system. In fact, here, adversaries can manipulate the system, can observe

and exploit the physical characteristics, and/or modify the physical inputs of the

system. These attacks require some specialized equipment and tools in order to

measure, modify and exploit the physical characteristics of the device.

Physical attacks can be divided into two main categories according to their level of invasion:

- Non-invasive: Non-invasive attacks interact with the physical device via its physical input and/or output characteristics (voltage, current, clock). These attacks can be passive and only observe and exploit some measurements, or can be active as well by modifying some of the characteristics. However, these attacks do not damage the system and usually do not leave any evidence of the attack on the system.

- Invasive: Invasive attacks on the other hand, require direct access to the inside of the device. Some of these attacks can result in irreversible damage and usually, they leave evidence on the system.

- Software or logical attacks: these attacks do not require any physical access to the system. Here, the main requirement for the attacker is to be able to run his code on the victim's machine.

In the TSUNAMY project, it is considered that the system is remotely used, for example in a cloud environment. Consequently, potential adversaries do not have any physical access to the system and are thus enable to launch physical attacks. Therefore, from now on, we focus on logical attacks only. Based on this scenario, only the software is considered as potentially malicious. The considered threat model is explained in Section 1.2.3.

#### Threats considered in the TSUNAMY project

Threats considered in the TSUNAMY project are classified according to the threaten security property.

Threats on the availability: Attacks threatening the availability of the system are known as Denial of Service (DoS) attacks. These attacks are intended attempts to stop legitimate users from accessing a specific shared resource preventing them to properly execute. In [17], two main methods to launch DoS attacks are described. The first one consists in sending some malformed data to the victim process in order to confuse a protocol or a running application. A second method aims at disrupting a legitimate user's connectivity by exhausting network or server resources, such as bandwidth, router processing capacity, CPU, memory and disk. For example, one malicious application can request an infinite amount of physical resources in order to endlessly hold the maximum amount of resources.

In this way, other applications cannot use these shared resources and must wait to be able to execute. Under a DoS attack where a malicious process continuously sends traffic to the shared communication infrastructure or services requests, a *non-protected* target system would respond considerably slow or even crash [17]. Finally, concurrent processes, remotely controlled and well organized, can collaborate in order to gain efficiency.

Threats on the integrity: Threats on the integrity concern the unauthorized access by writing data in memory. Malware such as trojan horses and rootkits can try to gain access rights in order to modify data in memory. A malicious process could make a huge number of requests of writing in memory which can cause the overstep on a different process memory region. This can result in unauthorized memory writing.

An attacker can exploit a programming error in a privileged service (e.g., OS services) in order to acquire privileges such as elevated accesses to a normally protected resource or information (privilege escalation) [18]. As a result, the attacker could threaten the availability, confidentiality and/or integrity of the system.

Threats on the confidentiality: Similar to threats on the integrity presented above, threats on the confidentiality target the unauthorized data access, this time by reading it. In the same way as for integrity threats, malware can try to bypass some security policies as well to achieve a privilege escalation.

The MMU and Secure Memory Protected Unit (MPU) are two widely spread countermeasures addressing unauthorized direct access, either by writing or reading, to data in memory. The principle is to verify, at runtime, the respect of access rights for each memory transaction. In this way, processes trying to access some data without having the corresponding right are prevented. If these mechanisms counter unauthorized direct access to data, indirect accesses, through the exploitation of leakage of information, are still possible.

In fact, an attacker process sharing the physical system with a sensitive one, could access and exploit some remanent information after the execution of the victim. Remanent information concerns memory, registers and buffers among others. One solution to avoid remanent information is to clear all the resources used by a sensitive application after its execution.

However, other attacks called SCAs, exploiting a different type of leakage, are more complex and difficult to prevent. These attacks can be physical or logical. As explained above, we focus on logical attacks only. Attacker processes launching logical SCAs observe some information about the victim process such as its execution time and memory access

| Mean of threat  | Logical attack                                       |

|-----------------|------------------------------------------------------|

| Availability    | DoS attacks:                                         |

|                 | - Communication bandwidth                            |

|                 | - Services requests                                  |

| Integrity       | Unauthorized direct access by writing data in memory |

|                 | - Privileges escalation                              |

| Confidentiality | Unauthorized direct access by reading data in memory |

|                 | - Privileges escalation                              |

|                 | Unauthorized indirect access by reading:             |

|                 | - Exploitation of remanent data                      |

|                 | - SCAs                                               |

Table 1.1 – Categories of logical attacks according to the threaten security property

patterns in order to deduce some more important information such as secret data or the performed instructions by the victim. These attacks are further explained in Section 1.2.4.

Table 1.1, summarizes the different categories of logical attacks according to the threaten security property.

#### 1.2.3 Threat model considered in this thesis work

The TCB defines the trusted, software and hardware, part of the system on which security policies rely. Therefore, in order to minimize the attack surface, it is important to reduce as much as possible the TCB.

The TSUNAMY project considers that the TSAR architecture is likely to be remotely used, in a cloud environment for instance. It is thus assumed that potential adversaries do not have any physical access to the hardware and therefore cannot compromise it nor launch any physical attack against it. Consequently, all the hardware components are included in the TCB, and only logical attacks are considered.

Applications, external to the system, are always considered as potentially malicious. Moreover, several malicious applications could collaborate in order to attack the system or to attack a concurrent application.

Two scenarios according to the definition of the TCB are distinguished.

The first scenario considers that the entire OS running on the platform is trusted. In fact, in this case it is assumed that the OS kernel services do not include all the features of an entire OS but are restrained to the services necessary for the dynamic deployment of applications and management of resources. In this scenario, only applications running

on the platform are considered as potentially malicious. The OS kernel being trusted, a malicious application can launch attacks against another application but cannot tamper with the OS. Security can thus rely on OS secure-enable mechanisms.

In a second scenario, the OS is not entirely part of the TCB. In fact, here it is considered that, in addition to applications, some OS kernel services can be compromised as well. In this case, it is still required that there is a trusted entity, that can include some OS kernel services or a hypervisor, responsible of ensuring the security policies of the platform.

Finally, concerning both scenarios, there have been some efforts in order to reduce the OS kernel code in the TCB by performing some functionalities, traditionally accomplished inside the kernel, in an outside unprivileged service component. For instance Linux provides a standard User I/O framework for developing user-space-based device drivers. Moving the device drivers into the user space can be done in a security purpose in order to reduce the size of the kernel. Recently, in [19], authors explore this approach.

In this work, the first scenario in which the OS kernel is entirely included in the TCB, is considered. Furthermore, this thesis work considers the execution within one VM and assumes that VMs are securely deployed by the hypervisor which guarantees the non interference between them [13]. Moreover, this work focuses on threats on the confidentiality and integrity and relies on the TSAR architecture supporting an MMU per processing core. The MMU prevents the unauthorized direct access to data in memory by reading and writing. Therefore, among other attacks considered in the TSUNAMY project, this thesis work specially focuses on unauthorized indirect access to data through SCAs. These attacks are further explained in the next section.

#### 1.2.4 Introduction to logical cache-based attacks

SCAs allow an attacker, which has no direct access to critical data, to analyze indirect or side-channel information during or after the execution of a sensitive application (e.g., a cryptographic algorithm) in order to deduce the sensitive application behavior or critical information such as a cryptographic key. Indeed, the implementation of software on the hardware introduces some physical measurements that can be exploited in order to deduce some information about the functioning of the victim's application.

Some examples of side-channels that can be exploited are power consumption [20][21], electromagnetic radiations [22], heat, sound [23] and time variations [24][25]. Depending on the side-channel information to exploit, the attacker may or may not require physical access to the system. We focus on attacks which do not require any physical access (see

Section 1.2.3) but shared physical resources between victim and malicious applications and that exploit time variations. These attacks are called logical or software cache-based SCAs. Especially, we focus on logical attacks that see the cache as the source of leakage. These attacks are not new. In 1998, authors in [26] introduced the prospect of attacks based on cache hit ratio in large S-box ciphers. Today, these attacks are still used and improved [24][25][27][28][29][30][31][32][33][34][35].

The cache is indeed a resource that several concurrent processes, sensitive and potentially malicious, compete for. When shared with an adversary, this latter can extract some information about the victim's activity that can be used to perform cryptanalysis.

These attacks can be performed at different granularities. First, these attacks can be performed within a single core when the victim and attacker processes execute on the same core and share the L1 cache [29]. Second, these attacks are also possible across cores when the victim and attacker execute on different cores but share the L2 or L3 cache (i.e., the LLC). Furthermore, these attacks can be performed across VMs in a cloud environment. In fact, a malicious application can perform these attacks against another application on a different VM despite VMs' logical isolation [31][30][32]. These attacks can steal sensitive information from systems implementing logically isolated execution environments [36]. These attacks, originally performed on desktop computers, have recently been extended to NoCs within shared memory Multiprocessor System-on-Chip (MPSoC) [37]. However, these have not been proved on NUMA systems such as the considered system in this work.

Cache-based attacks may be sophisticated, but their underlying idea is relatively simple: an attacker observes cache-based side-channel information such as the victim's execution time or memory accesses in order to gain information about the victim process sensitive data. Additionally, if the attacker can run code on the victim's machine, as well as manipulate the state of the cache, he/she is able to gain some extra information. By exploiting this knowledge, the attacker can retrieve confidential data of the critical program [38].

In state-of-the-art publications, cache-based SCAs are classified as time-driven, trace-driven or access-driven attacks based on the type of information the attacker learns about a victim process [24] [25] [27]. In trace-driven attacks, the attacker learns the outcome of each of the victim's memory accesses in terms of cache hits and misses [39] [28]. Extracting the trace of cache hits and misses in software represents a great difficulty. Consequently, trace-driven attacks are mostly performed in hardware and are thus out of the scope of this thesis work (Section 1.2.3). We thus focus on time-driven and access-driven attacks.

#### Time-driven attacks

These attacks exploit the vulnerability that, for some algorithms, the execution time is directly related to sensitive data. Moreover, attackers can exploit the fact that the execution time of an application is influenced by the current state of the cache leading to potential leakage of information. There are two categories of time-driven attacks; passive and active. The difference between these two is the location of the attacker. A passive adversary does not have access to the victim's machine and thus, cannot manipulate the state of the cache directly. Here, the attacker process triggers the sensitive application (e.g. an encryption algorithm) a certain number of times and measures the execution time. This latter is influenced by the state of the cache, which is itself influenced by each sensitive application execution. These attacks need more samples than active ones and often require statistical methods in order to successfully retrieve the sensitive information (e.g., the cryptographic secret key). In [40], for instance, a passive time-driven attack is remotely performed on AES algorithm. On the other hand, an active attacker has access and is able to run code on the victim's machine. This allows him to directly manipulate and probe the state of the cache by filling it with its own data or by evicting some specific cache lines. Here, the attacker can trigger the sensitive application, manipulate the state of the cache and measure the execution time. This gives to the attacker additional cache information, compared to passive attacks, and leads to more efficient attacks. A well known technique of this category is the EVICT+TIME presented in [41]. Authors perform an active timing attack on AES showing its efficiency compared to the passive attack presented in [40].

Here, the attacker is able to trigger the AES encryption and to know when it has begun and ended. It is also assumed that the attacker has the knowledge of the virtual memory address of AES lookup tables (T) using input-dependent indices, denoted V(T). Given a chosen plaintext p, one measurement routine for the attacker proceeds as follows:

- (a) Trigger AES encryption of the chosen p,

- (b) (EVICT) Access some memory addresses, B bytes apart, congruent to V(T),

- (c) (TIME) Trigger a second encryption of p and time it.

This routine is repeated a certain number of times. The measured time will depend on the plaintext, chosen by the attacker, and on the state of the cache, which is manipulated by the attacker at each routine. By analyzing results, the attacker is able to know which pages eviction influenced the victim's execution time, which will indicate that these pages were accessed by the victim.

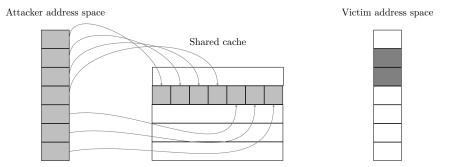

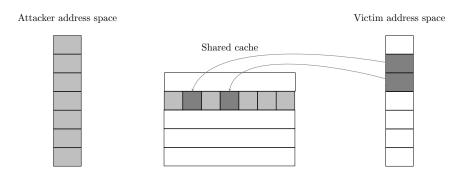

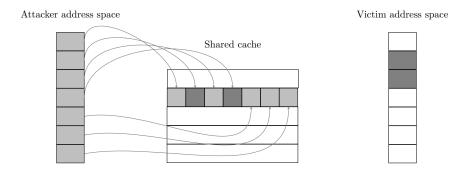

(a) PRIME step: The attacker fills the cache with its own data

(b) Wait step: Let the victim access some cache lines during the sensitive computation, consequently, some attacker data will be evicted

(c) PROBE step: Access to data and time. Access to data in cache (light gray lines) will take less time than accessing to data not longer in the cache after being evicted by the victim process (dark gray cache lines)

Figure 1.4 – Principle of PRIME+PROBE [29] attack

#### Access-driven attacks

In the same way as active time-driven attacks, access-driven attacks rely on the fact the attacker has access to the victim's machine and that there is a shared cache between the attacker and the victim processes. In fact, these attacks exploit the vulnerability that, for some systems, some instructions are related to sensitive data. The principle of these attacks is to deduce which cache lines the victim has accessed by directly manipulating and probing the shared cache and observing the memory access time. This additional information about the victim's cache access patterns makes these attacks more efficient than time-driven attacks.

The PRIME+PROBE [29] is a well known technique. Assume that an attacker manipulates the state of the shared cache by accessing some specific memory addresses, thus, filling the cache with its own data (PRIME). Then, the victim runs for a certain time and potentially changes the state of the cache. Finally, the attacker measures the time to access the same memory addresses again (PROBE). A short access time would indicate that the attacker's data is still in the cache (a cache hit) and thus that the victim has not accessed this cache memory line. On the contrary, a large access time would indicate a cache miss which indicates that the victim has accessed the same cache memory line. By exploiting this technique, the attacker infers information about the memory locations accessed by the victim, and thus the instructions or data that have been accessed.

The attack routine, illustrated in Figure 1.4 proceeds as follows:

- (a) (PRIME) Fill the cache with its own data,

- (b) Wait for the victim to execute and to potentially access some cache lines

- (c) (*PROBE*) Access to data and measure the access time in order to determine which cache sets have been accessed by the victim.

Finally, these attacks can be performed both, when the attacker and victim processes execute within the same execution core, as well as when they execute on different cores.

Among the same execution core: Initially, cache-based attacks were performed through L1 caches. In fact, access-driven attacks can be performed in multithreaded system when two processes, an attacker and a victim processes, are concurrently running on the same core and thus share the same L1 cache. In [35], authors demonstrated this technique on a 128-bit AES implementation of OpenSSL 0.9.8n on Linux.

Across-cores: The focus of cache-based attacks has shifted from first-level to shared LLC [30] [42] [33], enabling to perform these attacks across cores. The FLUSH+RELOAD